Hi all,

I was performing a test according to standard 60601-2-47 chapter "201.12.4.4.106 System noise". I am using two inputs in my setup.

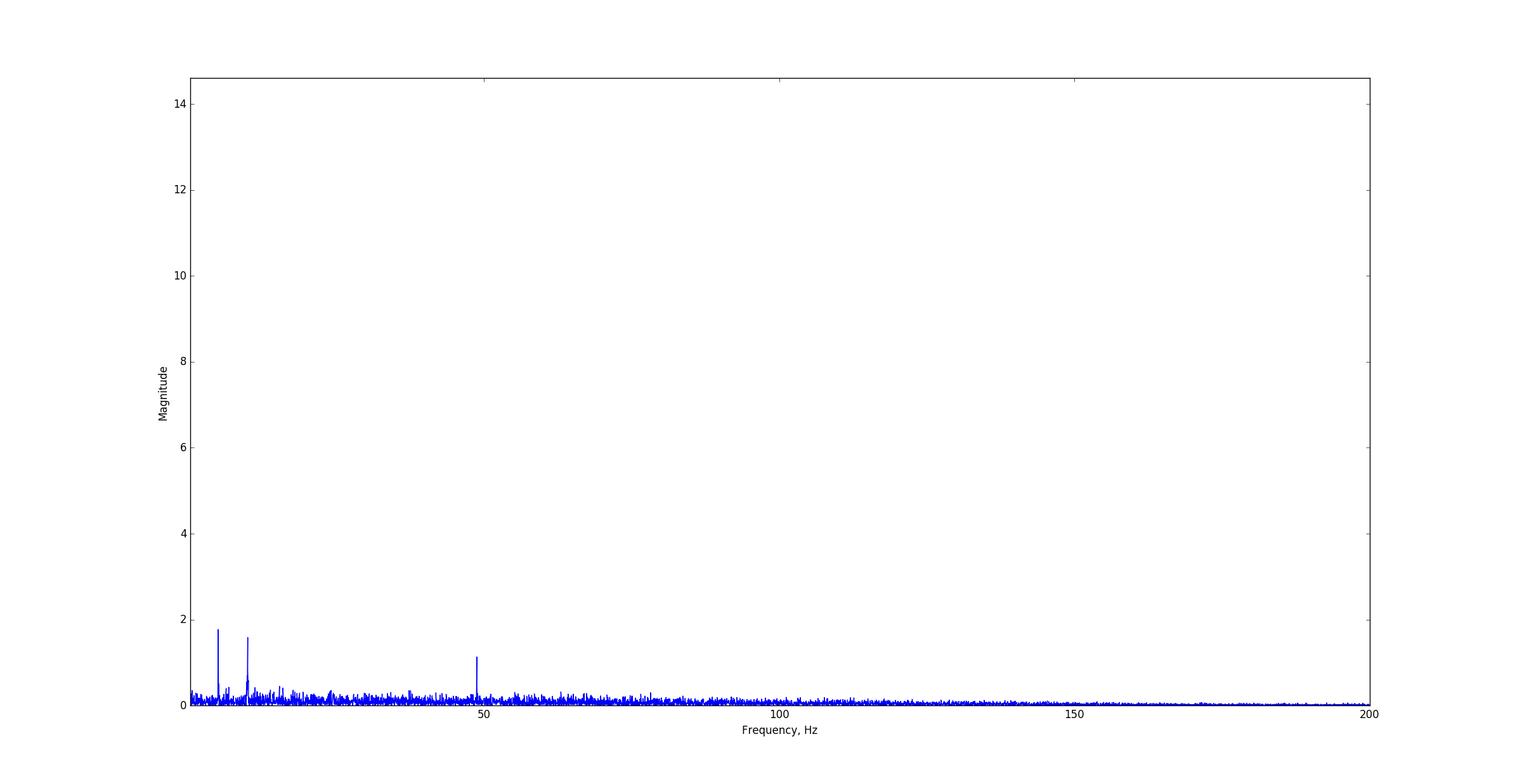

When I don't enable RLD, I get ~10uVp-p noise, but when I enable RLD on one of the two inputs, I get much larger noise - about 80uVp-p this is much bigger than 50uVp-p quoted in the standard. How come RLD injects so much noise? Can I avoid it? I am attaching all the related info I have.

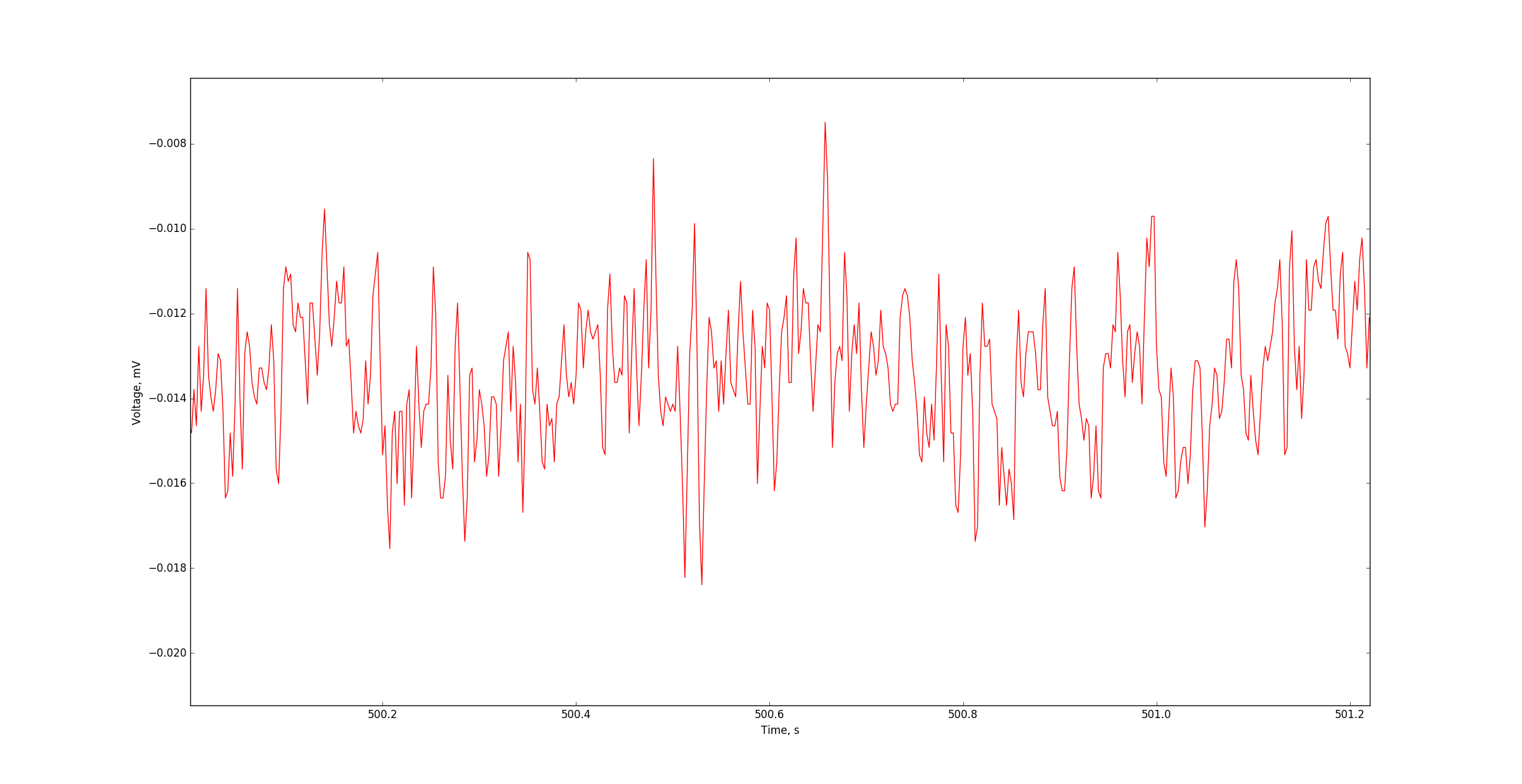

System noise with RLD off:

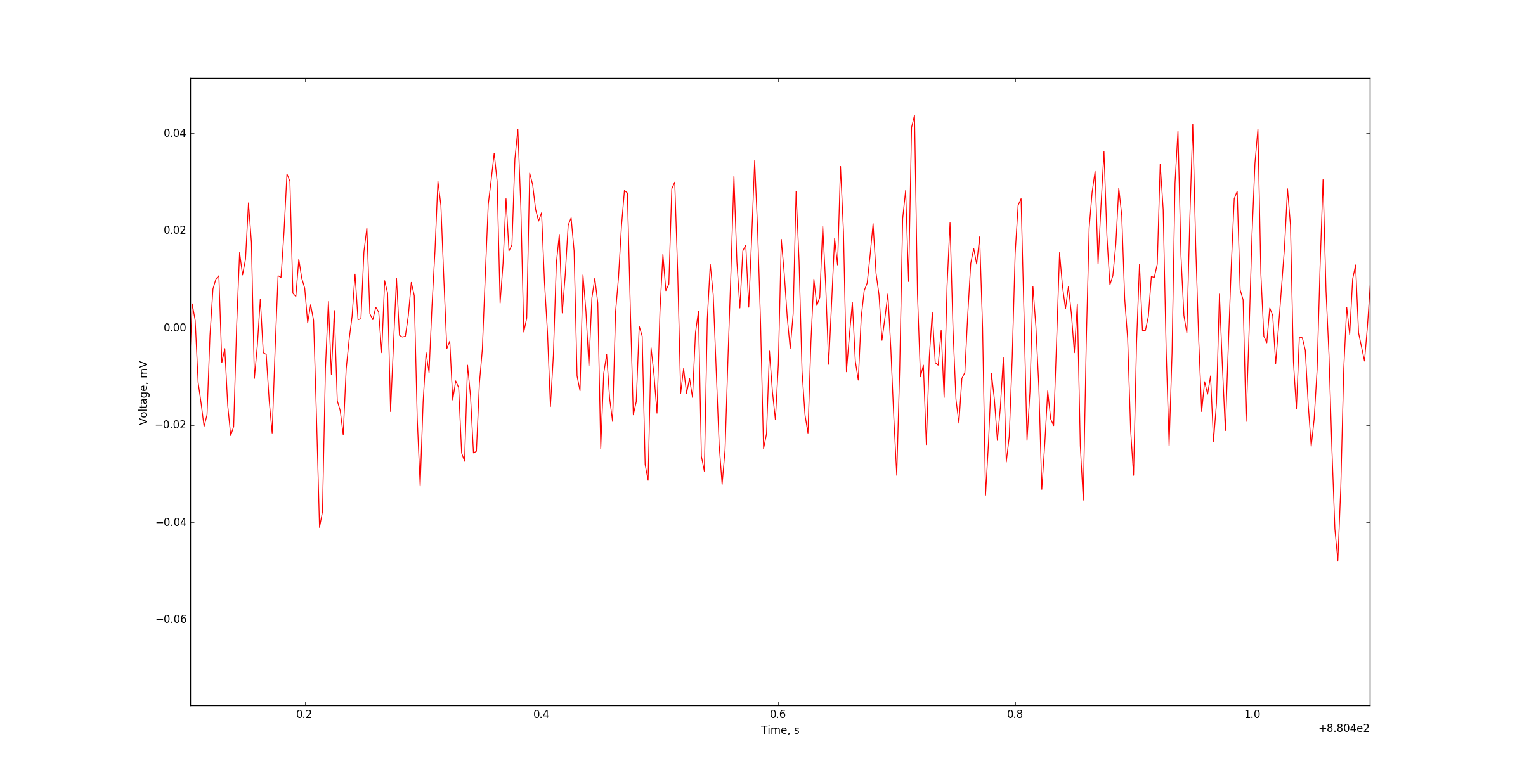

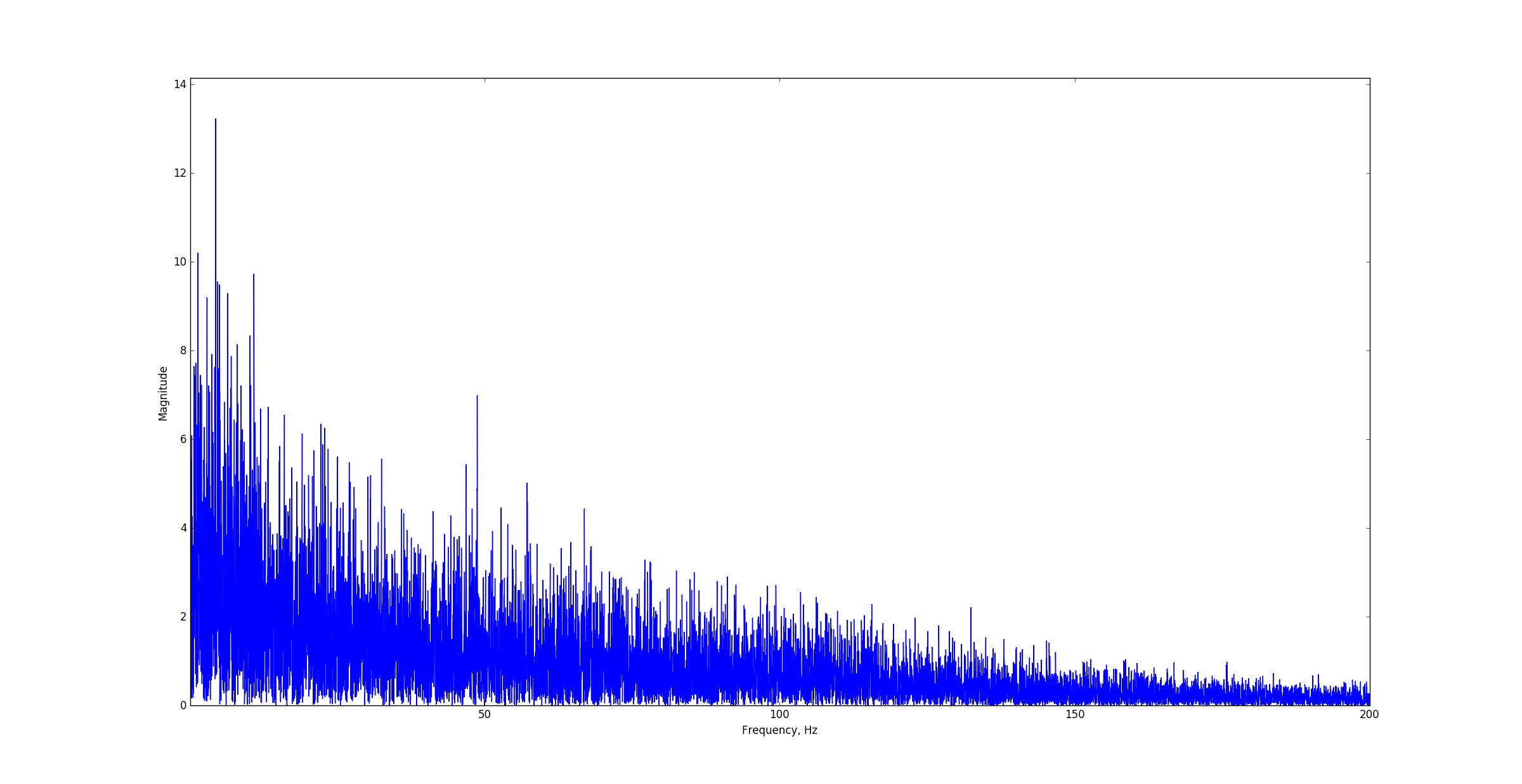

System noise with RLD on:

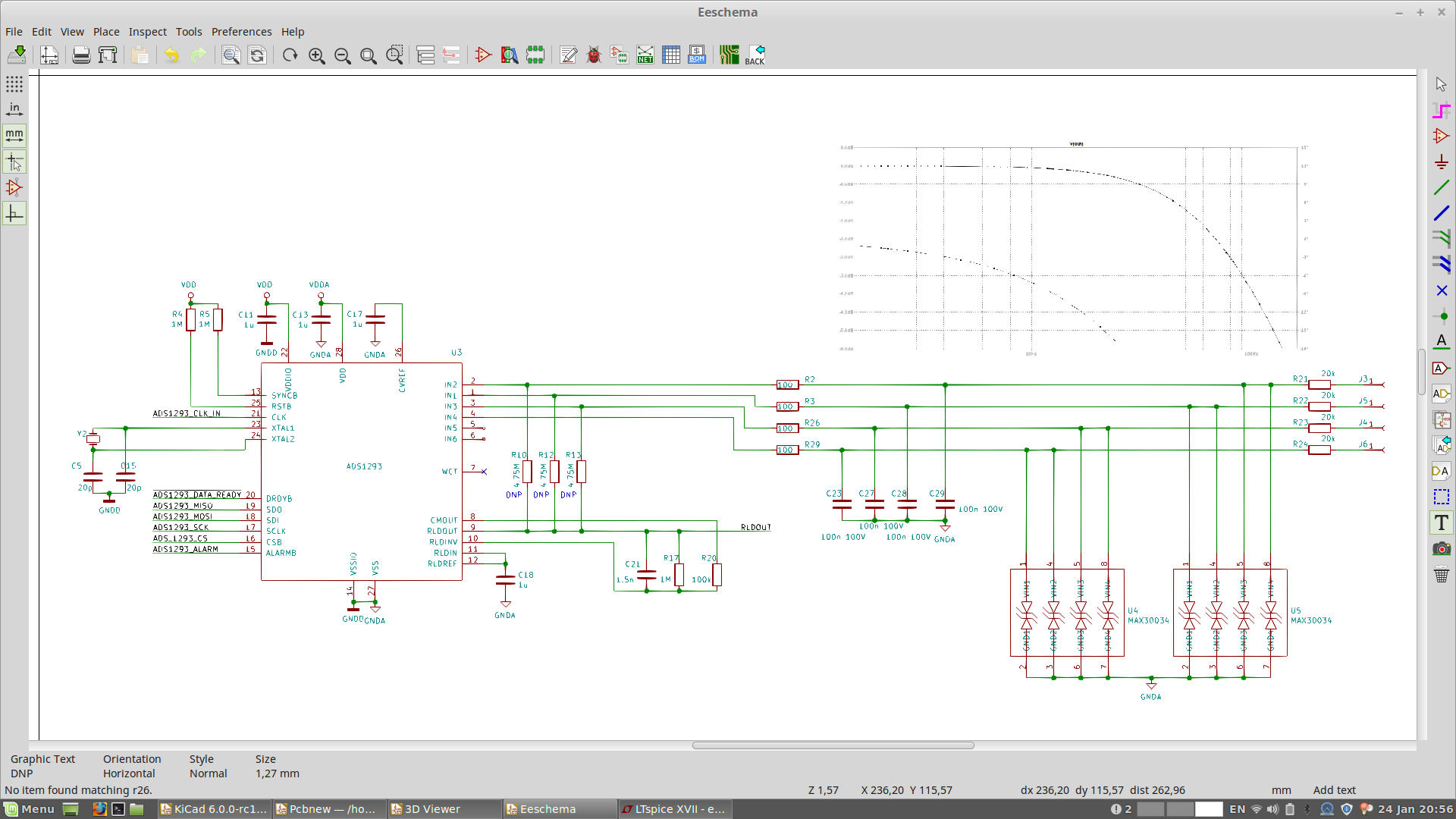

Schematics:

ADS1293 config:

{FLEX_CH1_CN, 0b00011010}, //0x01 POS - IN3, NEG - IN2

{FLEX_CH2_CN, 0x00}, //0x02

{FLEX_CH3_CN, 0x00}, //0x03

{LOD_CN, 0b00001000}, //0x06 DC lead off detection - OFF

{LOD_EN, 0x02}, //0x07 lead off detection on IN2

{CMDET_EN, 0b00000000}, //0x0a CM detection - OFF

{RLD_CN, 0b01110011}, //0x0c high BW, high cap dirve RLD on IN3

{AFE_RES, 0x09}, //0x13 high res 200kHz for channel 1

{AFE_SHDN_CN, 0b00110110}, //0x14 insta and modulator shutdown for ch2 and ch3

{CH_CNFG, 0x00}, //0x2f

{R2_RATE, 0x01}, //0x21 R2=4

{R3_RATE_CH1, 0x40}, //0x22 R3=64 400 samples/s 80Hz BW ADCmax = 0x800000

{R3_RATE_CH2, 0x01}, //0x23

{R3_RATE_CH3, 0x01}, //0x24

{R1_RATE, 0x01}, //0x25 R1=2 double pace rate for CH1

{DRDYB_SRC, 0x08}, //0x27 ch1 as DRDYB source

{FLEX_PACE_CN, 0x00}, //0x04

{FLEX_VBAT_CN, 0x00}, //0x05

{LOD_CURRENT, 0x0f}, //0x08

{LOD_AC_CN, 0x00}, //0x09

{CMDET_CN, 0x00}, //0x0b

{WILSON_EN1, 0x00}, //0x0d

{WILSON_EN2, 0x00}, //0x0e

{WILSON_EN3, 0x00}, //0x0f

{WILSON_CN, 0x00}, //0x10

{REF_CN, 0x00}, //0x11

{OSC_CN, 0x06}, //0x12

{AFE_FAULT_CN, 0x06}, //0x15 disable fault detection for CH2 and CH3

{AFE_PACE_CN, 0x01}, //0x17 analog pace shutdown

{DIGO_STRENGTH, 0x00}, //0x1F

{DIS_EFILTER, 0x06}, //0x26 filter disabled for CH2 and CH3

{SYNCB_CN, 0x00}, //0x28

{MASK_DRDYB, 0x00}, //0x29

{MASK_ERR, 0xff}, //0x2a

{ALARM_FILTER, 0xFF}, //0x2e