Other Parts Discussed in Thread: LMK04828

Hi Jim,

Still working on the ADS54J66. My goal is program my ADC over spi directly, but the address paging doesn't seem to agree with the .cfg files provided in the evm.

For the EVM, we were given this set of config files for use with the evm program tool:

""

ADS54Jxx_ANALOG

0x0000 0x81

0x8039 0xC0 // always write a 11 to bits 6-7

0x8053 0x80 // divide by 2 required for ADS54J66

0x8055 0x00 // must write 0

0x8056 0x00 // must write 0

0x8059 0x20 // must write a 1 to bit 5

ADS54Jxx_DIGITAL

0x6800f7 0x01 //digital top reset

0x680000 0x01 //reset digital

0x680000 0x00 //clear reset

0x614100 0x02 // dec filter page mode 2

0x614101 0x00 // 0 for LPF, 1 for HPF CHB & C

0x614102 0x00 // bit 5, 0 for LPF, 1 for HPF CHA & D

0x690000 0xC0 //set CTRL K + control mode

0x690001 0x02 // JESD mode 40X

0x690006 0x04 //set K to 5

0x6A0016 0x02 // JESD PLL Mode 40x data sheet typo???

0x6A0017 0x40 // PLL reset

0x6A0017 0x00 // PLL reset release

ADS54Jxx_LOWLEVEL

0x4004 0x69

0x4003 0x00

0x4005 0x01 // disable broadcast mode

"" You can see the full file attached below.

Where the address is in column 1 and the data is in col 2. This works great for us when using the gui.

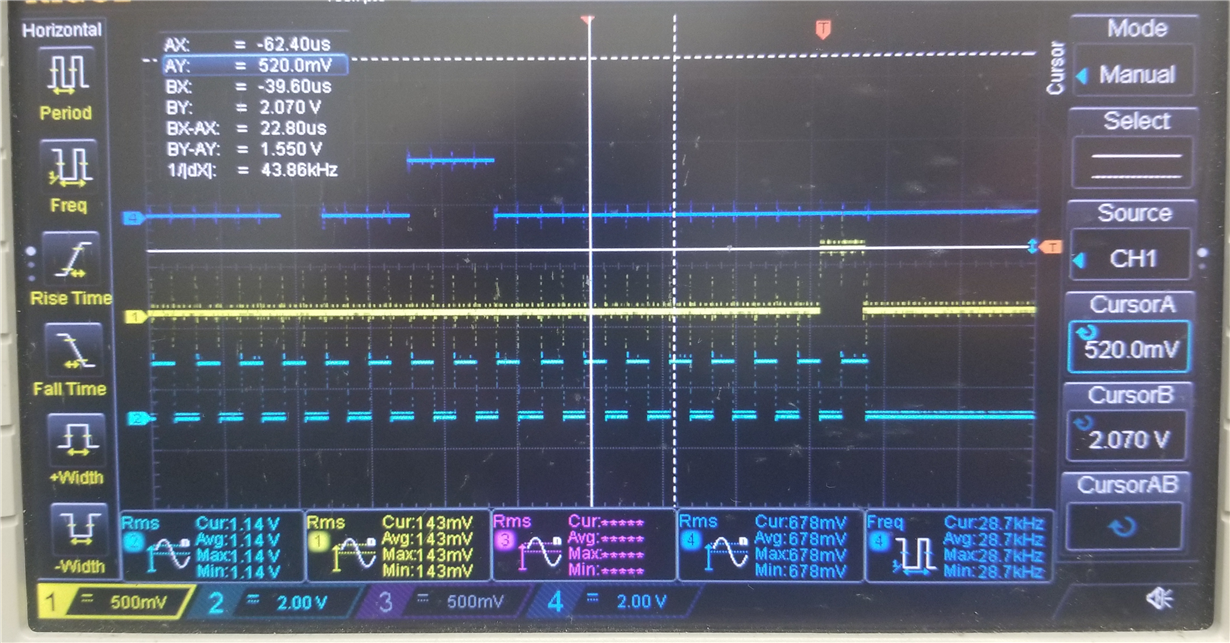

However, this cfg seems to not be a bit accurate representation of what is being sent out over the spi line to the ADC. In the data sheet, a single spi transaction is 3 bytes, 24b long, where this shows an extra address byte in the digital config. I know there's page access writes, which appear to be being abstracted by the ADS gui. I cannot probe the spi lines directly b/c the EVM doesn't have test points.

Is there a way to get a bit accurate representation of whats going on here? Or, put another way, how can I translate the above file into spi transactions that are only 24b long?

Thanks for the help,

-Jake