Other Parts Discussed in Thread: TMS320C5535, , ADS131A04EVM

I'm currently trying to receive data from the ADS131A02DC, but am having a problem with the DRDY line. My hardware is set up such that M0 is HIGH (asynchronous interrupt mode), M1 is HIGH (32 bit), and M2 is LOW (hamming disabled). I've managed to successfully write and read to the ADC registers and have read the STAT_M2 register to verify that my hardware is setup correctly (it is).

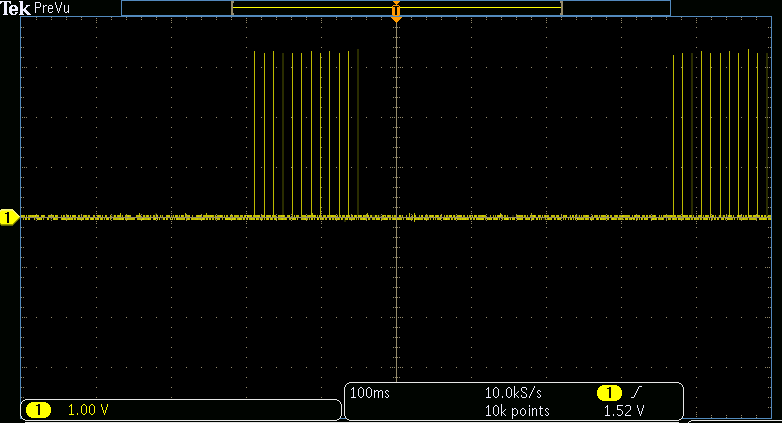

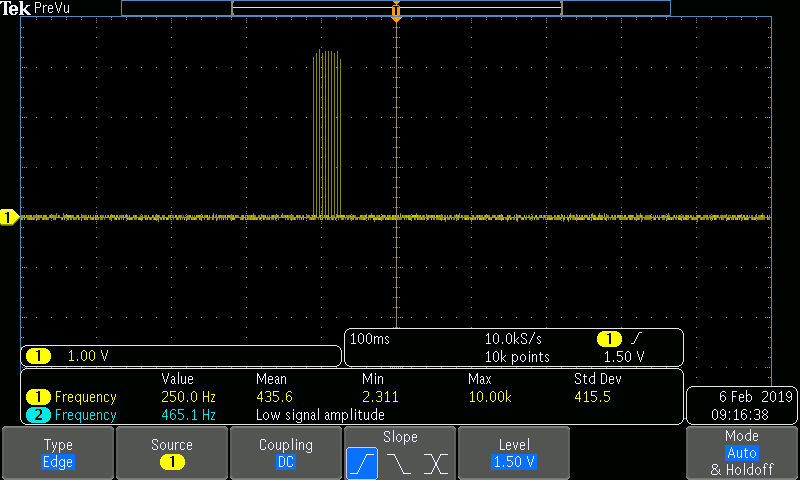

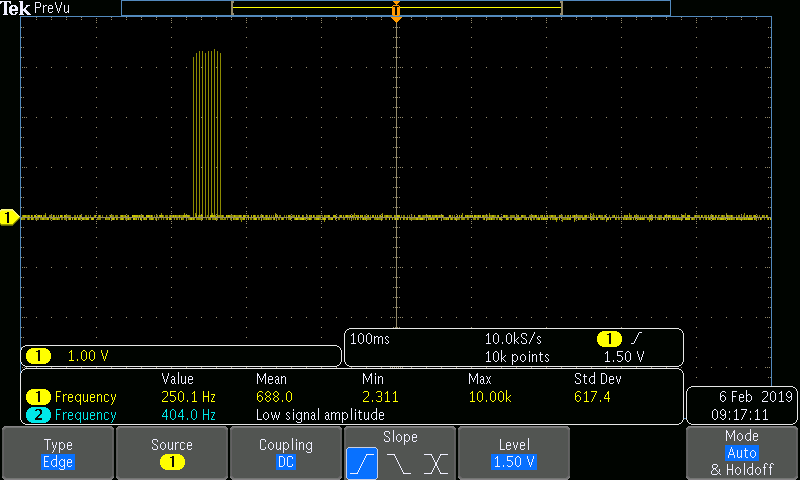

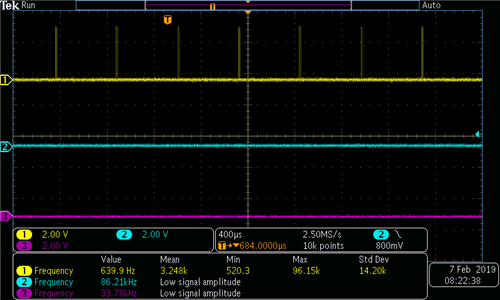

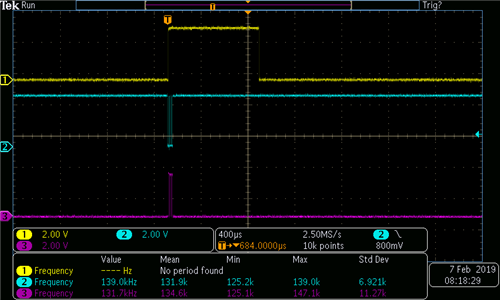

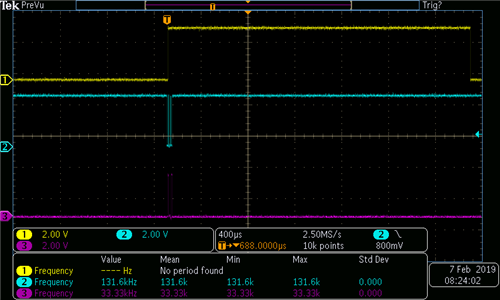

The DRDY line is suppose to be active low so I expect the voltage to be HIGH at 3.3V, but I'm seeing the following on the oscilloscope even though the ADC is in STANDBY MODE:

I was worried that the DRDY line needs to be driven with a pull-up resistor, so I attached a pull-up resistor to 3.3V but the problem persists. I have removed the pull-up resistor and am unsure what else could be wrong.

Communication is working fine, so I'm assuming DIN/DOUT/SCLK/*CS are all OK.

*RESET is pulled HIGH(3.3V)

*DONE is OPEN, but internally pulled-up HIGH(3.3V) within the ADC.

*DRDY is OPEN, for probing purposes. I expect a HIGH signal but am getting the signal shown above.

Any guidance and help would be greatly appreciated.