Other Parts Discussed in Thread: LMK04828

Hi

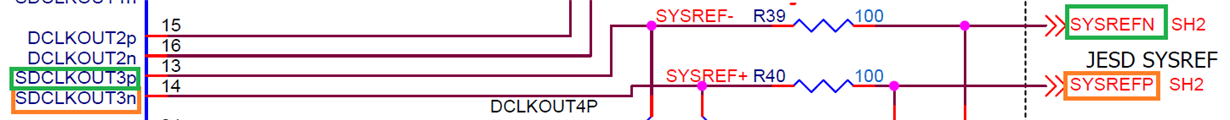

In the reference design for LMK04828 and DAC38RF8xEVM, sheet 5, the SYSREF (P, N) outputs are connected to the wrong pins on the device. SYSREFN is connected to SDCLKOUT3p and SYSREFP is connected to SDCLKOUT3n.

I wanted to evaluate the design with a FPGA board. I'm using Rev E schematic which I believe is the latest one. And since I couldn't find any question on this on the community, I assume that the the eval board functions as desired.

Can anyone kindly explain, how is it working even when it is connected in the wrong manner? And does TI know this and plans to correct the scehmatic?

Regards

Atin