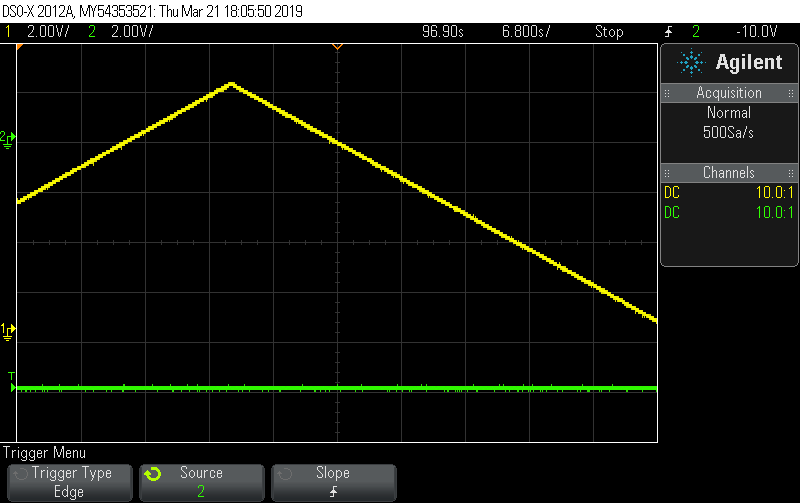

Hello everybody. I am using DAC7821 which is a 12 bit parallel DAC which is interfaced to Infineon XMC4800 microcontroller. I am using it as unipolar output of the range 0V to 10V. If I write the DAC code to DAC data register output is coming correctly. But if I write (9.98*409.6) to the register out put is zero. So the maximum output is 9.97.

But as per my understanding the maximum digital input you can given to the DAC is 111111111111 which corresponds to FFF. But in my case If I give 9.98 the corresponding digital code bit will be 111111110111 which comes below the maximum range. Am I understood it correct??