Hi everyone,

I apologize in advance for the length of this post but I think it's better to say something unnecessary than omit something useful.

We are trying to use an ADS131E04 and a STM32F4 microcontroller on our custom board to acquire data from a 3-axial analog accelerometer but we are experiencing some strange behaviour of the DRDY line.

All we need is 100Hz sampling rate so we are planning to configure the ADC to 1kSPS, RDATAC mode, software START and STOP commands (the START pin is tied low), and just ignore 9 out of 10 DRDY transitions.

We are able to communicate with the ADS, correctly write configuration registers and read them back.

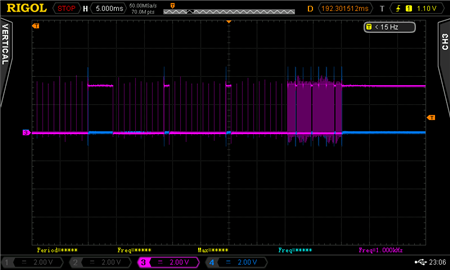

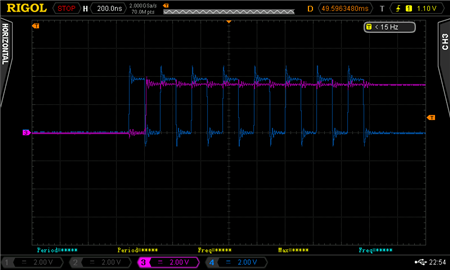

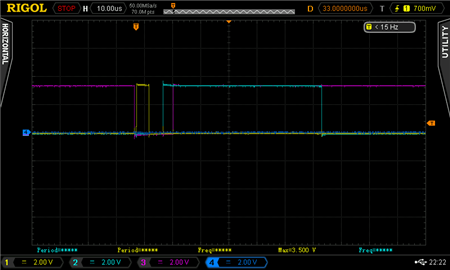

Now, as you can see from the first screenshot, when we issue a RDATAC command followed by START command, DRDY behaves correctly: there's a transition every 1ms (the line stays down because we're not retrieving data from SPI hence we're not issuing SCLK); but if we try to read the data (15 byte SPI read operation) then sometimes DRDY appears to slow down to one transition every 4.5ms (2nd screenshot).

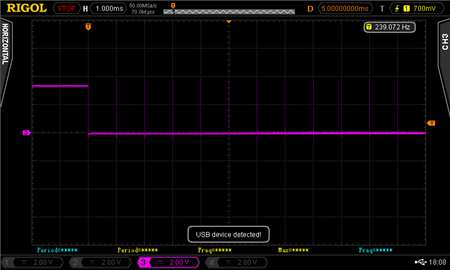

In the 3rd screenshot you can see the timing of DRDY (3-magenta), ISR semaphore unlocking (1-yellow) and SPI 15bytes read operation (2-cyan); just ignore number 4 (blue), I forgot to disable the line before taking the screenshot..

The retrieved data seem to be correct (in the sense that they follow the orientation of the sensor) so probably the problem regards just DRDY timing.The strange thing is that it doesn't seem to be precisely reproducible, it seems to have some kind of randomness because sometimes DRDY just stops "toggling" without issuing the STOP command.

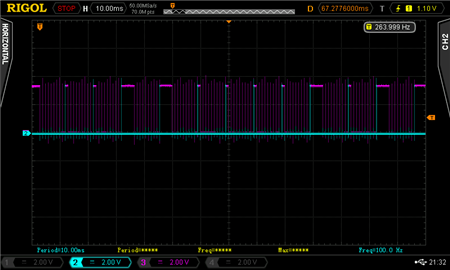

The 4th screenshot shows that when this happens, in the last acquisitions DRDY "toggles" at 16kHz instead of 1kHz (a kind of reset?! but the datasheet states that the module resets at 32kHz..).

If we try to read the configuration registers multiple times after DRDY stops, we see random values for few times and then some values that seem to be a "default" configuration.

Our configuration Random values "Default" configuration 0: 0xD0 0: 0x30 0: 0xD0 1: 0xD6 1: 0x4D 1: 0x91 2: 0xE2 2: 0x62 2: 0xE0 3: 0x61 3: 0x1D 3: 0x41 4: 0x00 4: 0x4E 4: 0x00 5: 0x10 5: 0x20 5: 0x10 6: 0x10 6: 0x76 6: 0x10 7: 0x10 7: 0x6C 7: 0x10 8: 0x90 8: 0x32 8: 0x10 9: 0x00 9: 0x00 9: 0x08 10: 0x07 10: 0x00 10: 0x07 11: 0x0F 11: 0xC0 11: 0x0F

The last screenshot is just to show that DRDY goes correctly high after the first SCLK falling edge.

We tried different configurations (sampling rates, spi speed...) without any result.

Have you ever experienced something like this? If it can be useful I can upload the part of the schematics regarding the ADS.

Thank you in advance for your help.

Best regards.

Mattia