Other Parts Discussed in Thread: ADS5294EVM, ADS5294

Hello,

I am trying to use ADS5294EVM with TSW1400EVM and I am running into a weird issue. I have the Quartus project file from TI and it compiles good. What I tried doing was convert to vhdl and simplify the code little bit. All the PLL and serdes were set up exactly the same way as the TI's firmware. DCLK(data clock) from the ADC board goes into pins AA7 and AA6 and this one drives a PLL and the output clock of the PLL (2*DCLK) drives the serdes input. When I try to compile the code I get the following error

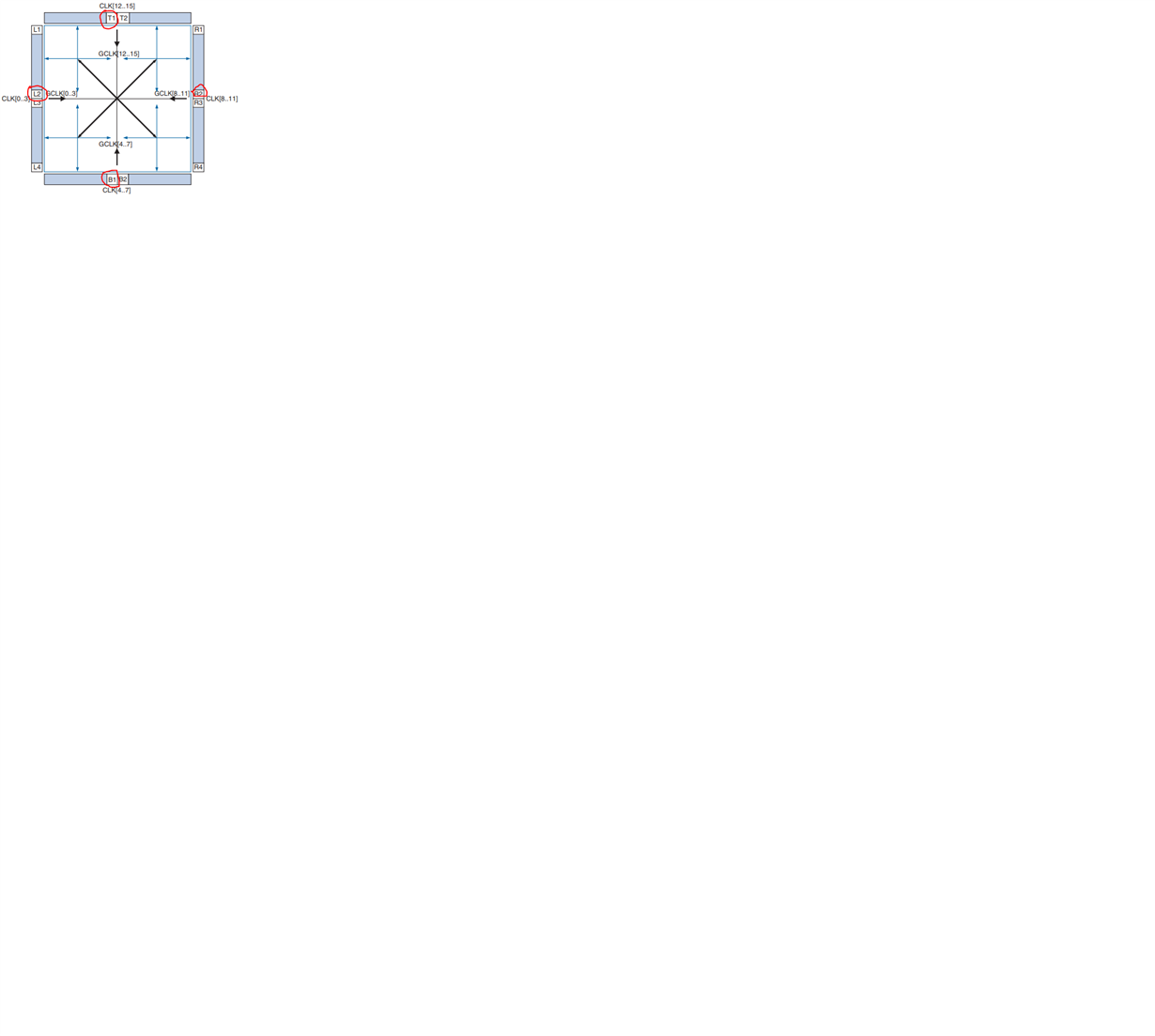

Error (176562): Can't place Left/Right PLL "pll_adc_data_acq:inst24|altpll0:adc_pll_config|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1" in PLL location PLL_B1 because the location does not accept Left/Right PLLs

Error (176563): Can't place Left/Right PLL "pll_adc_data_acq:inst24|altpll0:adc_pll_config|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1" in PLL location PLL_L2 because PLL has a location assignment that is incompatible with the PLL location in the device

Error (176161): Can't place input clock pin clk_lvds_rx0_p driving fast PLL pll_adc_data_acq:inst24|altpll0:adc_pll_config|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1 in non-compensated I/O location AA7 -- fast PLL drives at least one non-DPA-mode SERDES

Error (176562): Can't place Left/Right PLL "pll_adc_data_acq:inst24|altpll0:adc_pll_config|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1" in PLL location PLL_T1 because the location does not accept Left/Right PLLs

not sure why am I running into this issue, as I am using exactly the same thing as the TI's firmware. Can someone from the firmware team look into it and please let me know, if I need to add anything to the constraints somewhere, so that it won't give an error with the compilation.

Thanks in advance

Regards,

Ramakrishna