Tool/software: Linux

Hello,

I am trying to measure the voltage at channel 0

CMD 0x97 represent below configuration.

7 Bit => Start Bit. Control byte starts with first HIGH bit - 1b

6-4 Bit => A2 - A0 Channel Select Bits - 001b (channel 0)

3 Bit => Mode - 0b (12Bit ADC)

2 Bit => Single-Ended Channel Selection - 1b

1-0Bit => Power-Down Mode No power down- 11b

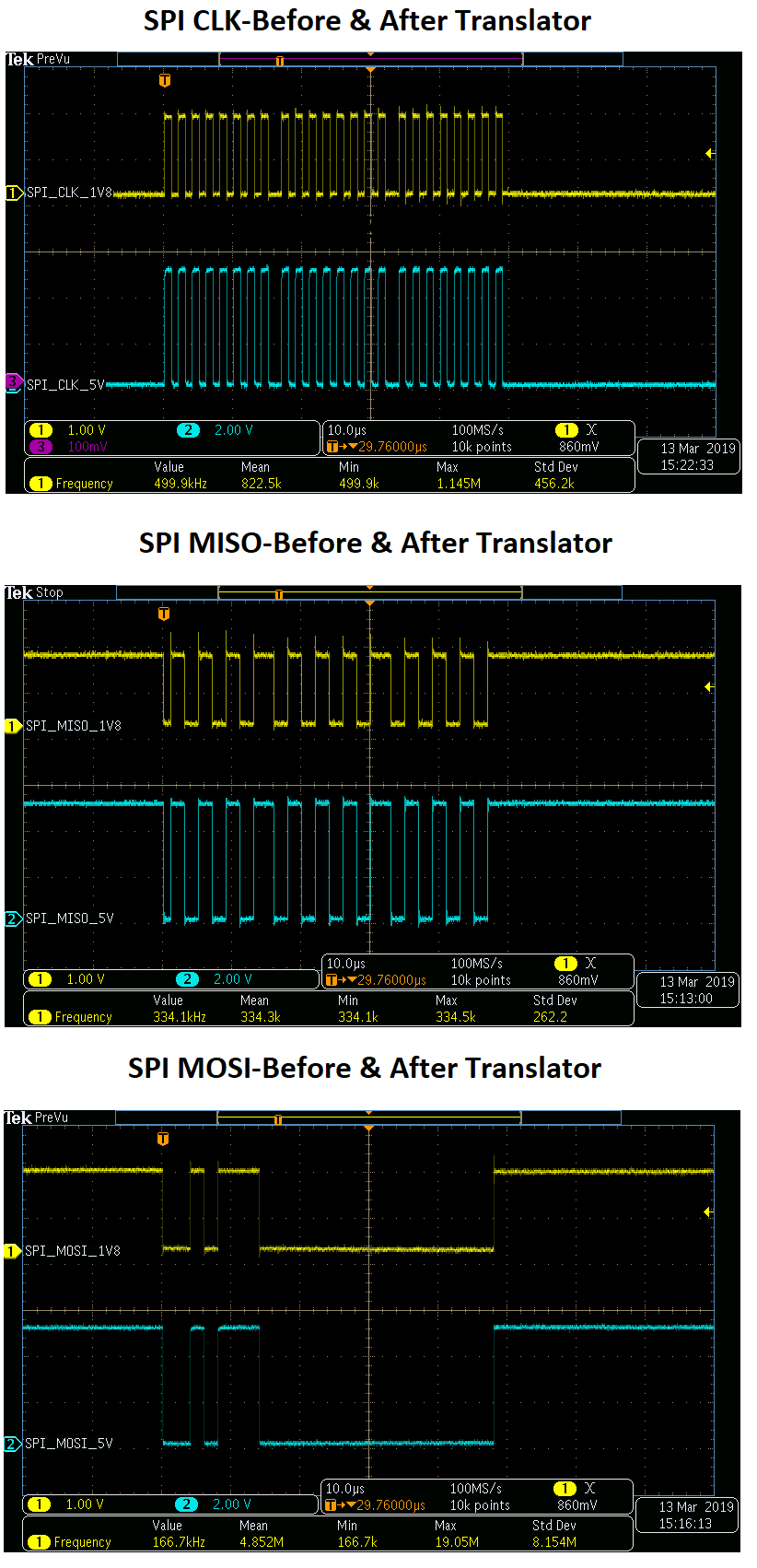

I am observing random values at MISO line. Could you please review the command value. Is there any test mode/command available to check validate the ADC chip response.

From your previous comments,

>>how many clocks per conversion are you sending?

How can I check the configured clock per conversion?