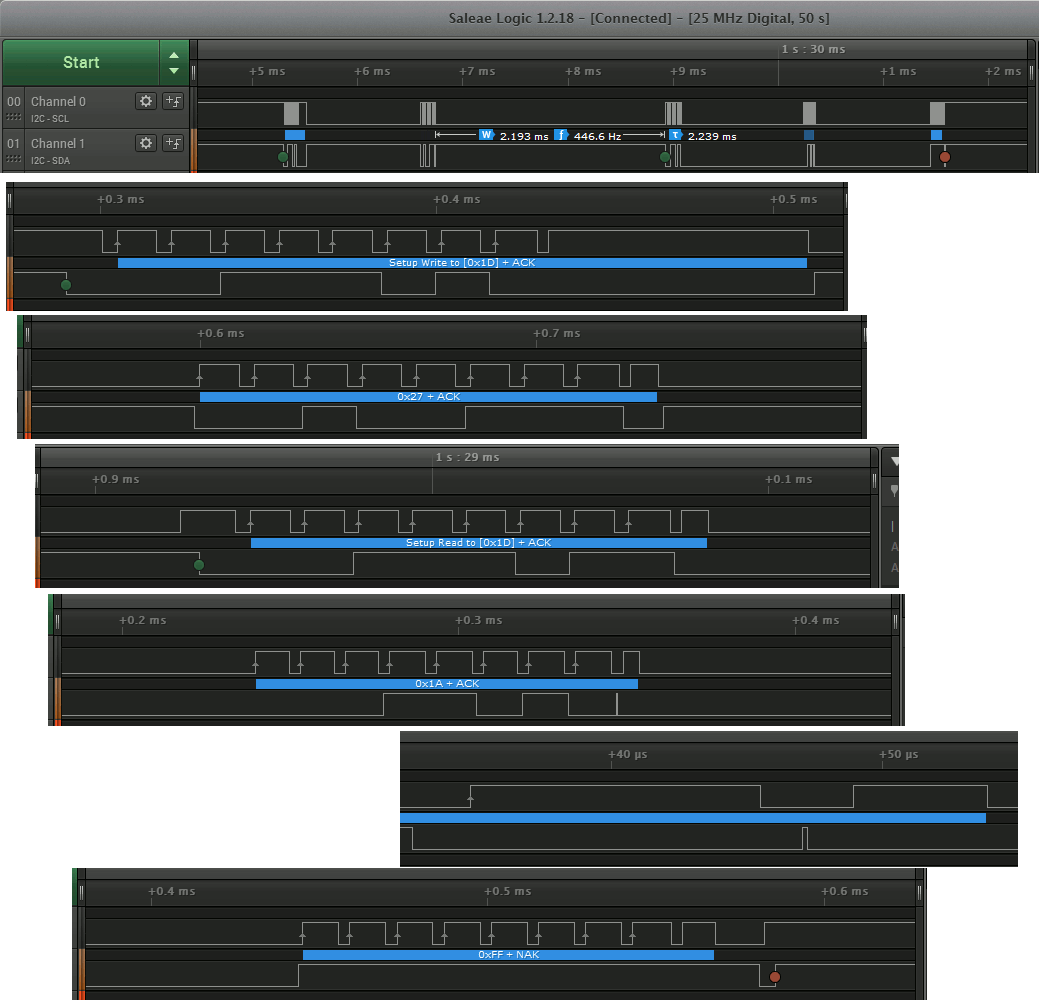

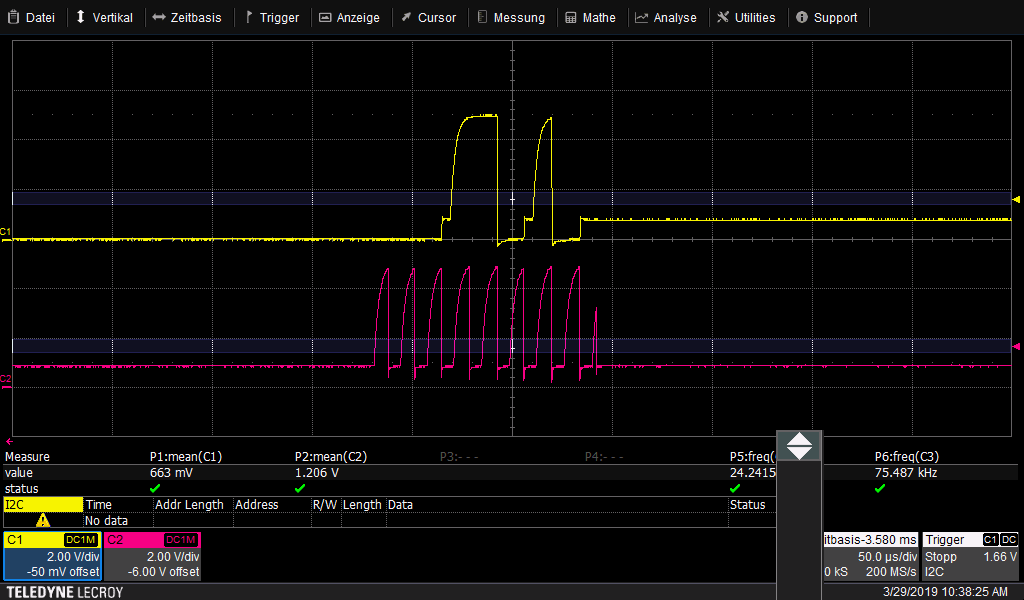

I set up a ADC128D818 to convert continuously in mode 2 (four differential inputs). The MSByte seems to be read correctly, but the LSByte sticks on 0xFF (on all four channels). Is there something I've forgotten, like switching to a 16-bit-mode?

Thanks in advance, Peter