Hello,

Our customer had been facing no /DRDY output problem of ADS12L01 at 384kHz or 1.536MHz CLK mode.

If we add capacitor to START pin to make some delay, it resolve the issue.

Could you please confirm following questions to know prohibit clock timing.

(ADC's working condition is 262kHz to 16.77MHz CLK input, 128/256OSR, HR/LP mode, SPI interface, +3.3V DVDD)

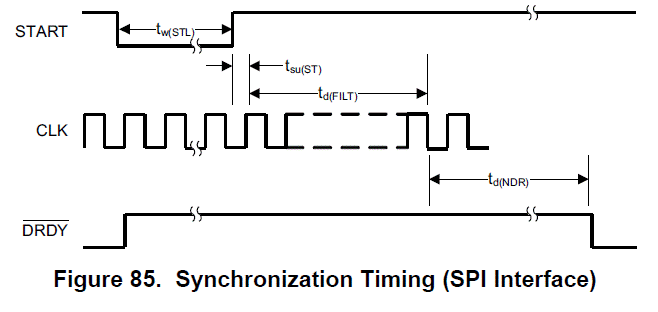

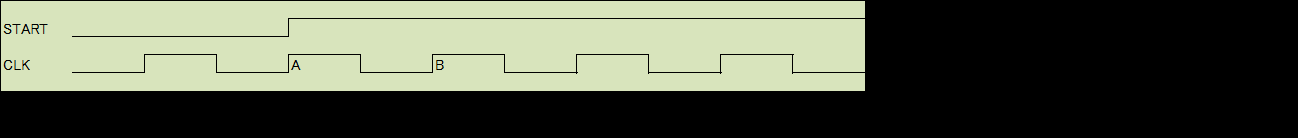

Q1: On the datasheet Figure 85 shown, START ramp up command is during CLK Low state with tsu(st) setup time requirement.

Then what happen if we send START command as Figure A, The ADC can recognize START command at next CLK ramp up as B point?

Q2: Is this DS ADC's internal state-machine run to output /DRDY to Low following tsu(ST) + td(FILT) + td(NDR) processing time after detect START command? No matter what is CLK status when send START command.

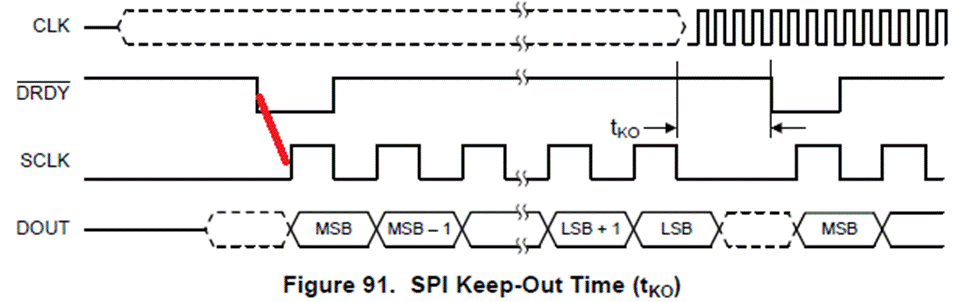

Q3: In Figure 91, what if we input SCLK clock during tko time period, Is the ADC output /DRDY Low correctly?

Q4: Is there timing requirement for "Red Line" period in Figure 91?

Regards,

Mochizuki