Hi Team,

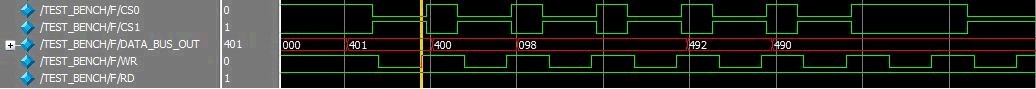

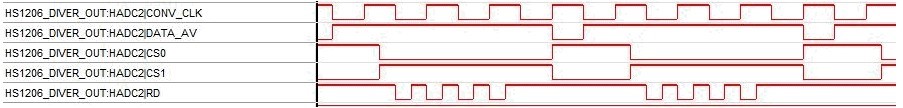

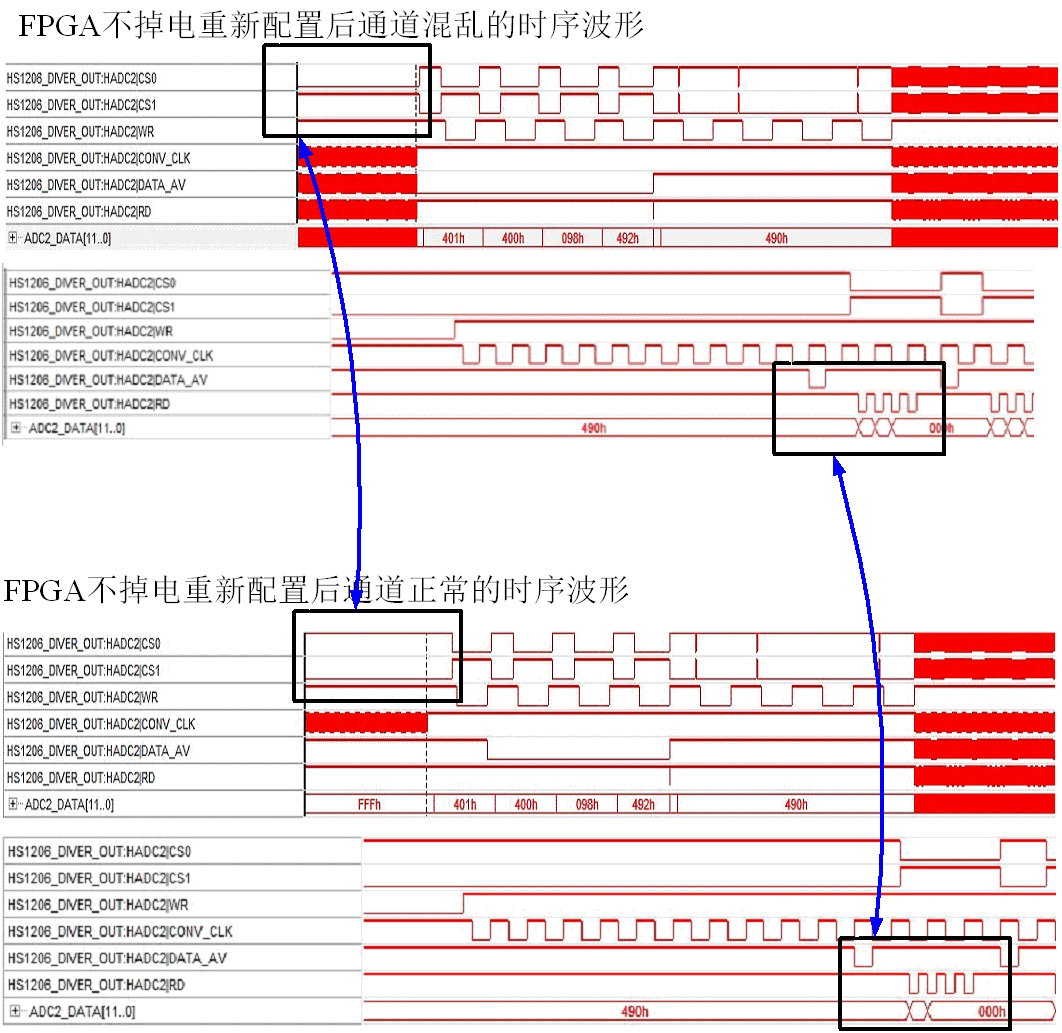

According to the description of DATASHEET, the first RD pulse output after the DATA_AV signal is channel 1, the second RD pulse output channel 2, third RD pulse output channel 3, and fourth RD pulse output channel 4.

Based on above timing control, the RD pulse after the DATA_AV signal does not correspond to the respective channel number.

When the power is initialized, the first RD pulse output channel 4, the second RD pulse output channel 1, and the third RD pulse output channel 2, fourth RD pulse output channel 3.

The data captured on CH1 is output on CH2 while the CH2 data is output on CH3.

Could you please help to advise how to solve this issue?

Thanks.