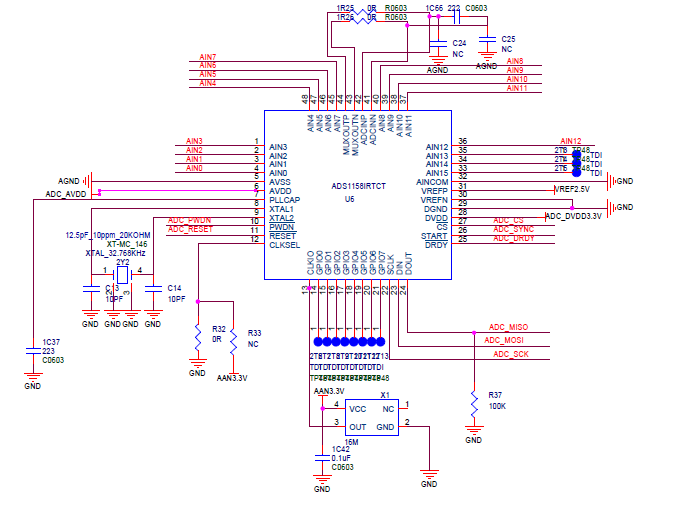

Part Number: ADS1258

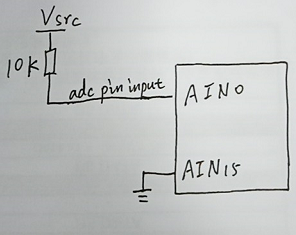

The sch is below.

Test enviromnet:

1. Crystal select: 32.768 kHz

2. AVDD: +5V, AVSS: 0V, VREFP: +2.5V, VREFN: 0V

3. Work mode: fix mode,

4. Channel select: P: AIN0 (adc sample input), N: AIN15(connect to GND)

5. Registe confog:

Test Case:

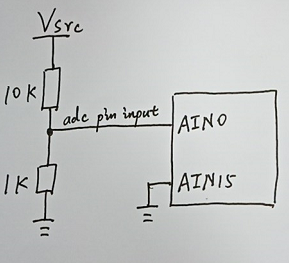

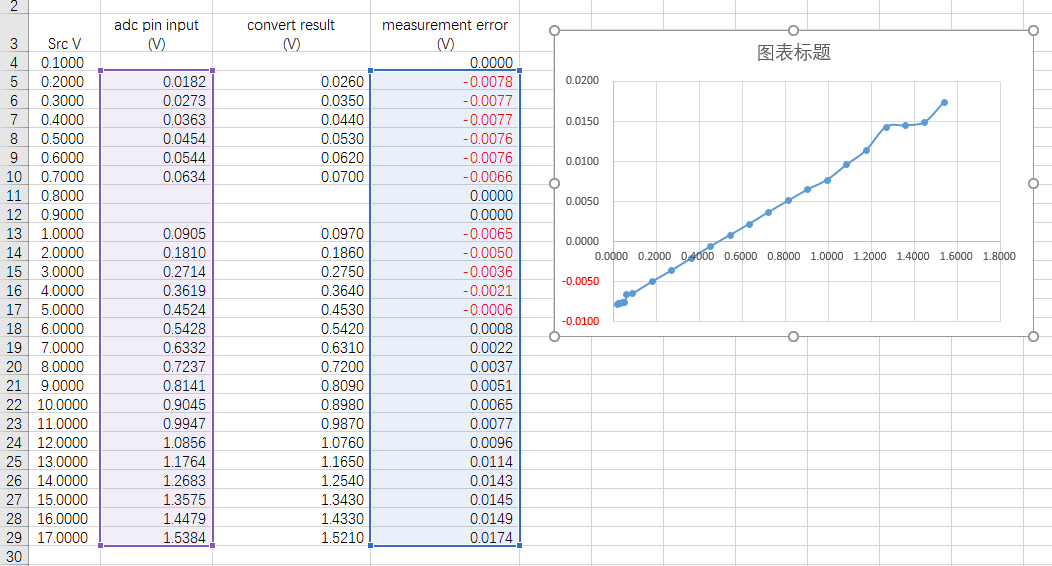

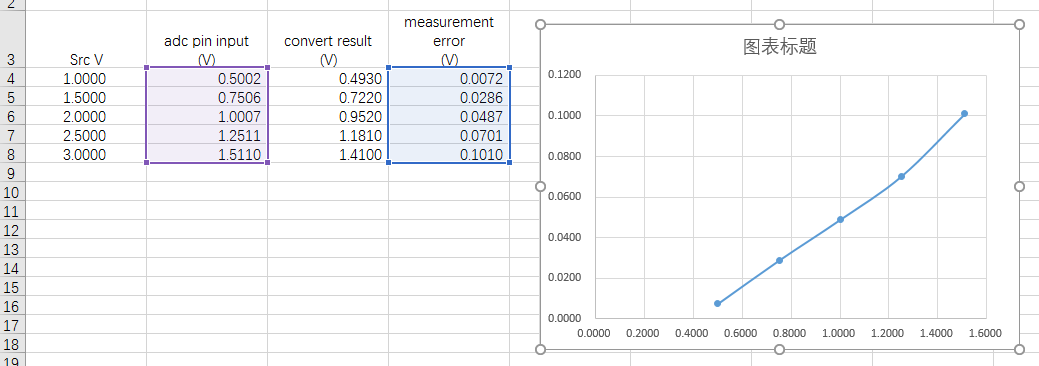

case 1: 10K/1K

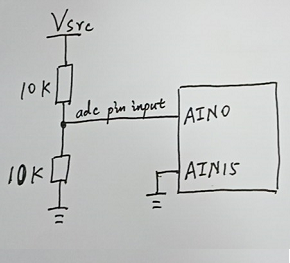

case 2: 10K/10K

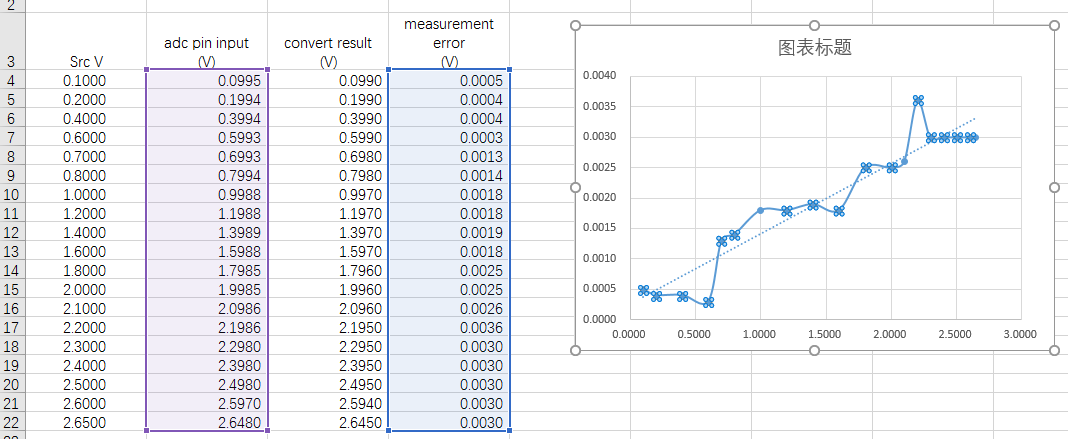

case 3: 10K/∞