Hi there,

I have an ADS8168EVM, which I have tested the functionality of, with a PHI controller. To make sure it works with my custom host (which is an Adafruit FT232H USB to SPI), I have brought out all the digital signals and hooked them up to the FT232H.

It seems that I am able to send command from this host correctly but I'm have trouble receiving data from the device correctly. I'm just performing basic register read / writes but it seems that the device toggles data on the clock rising edge, even though my mode is set to 00. Data is sent correctly on the rising edge from the host.

As an example, I write 3 bytes each time.

First time, I write to Register 00h using the write command, the value 0xAA ([0x8, 0x0, 0xAA])

Then I read from this register using the read command as per below ([0x10, 0x0, 0x0])

I should just get 0xAA on the SDO line at this point but I tend to get garbage bits.

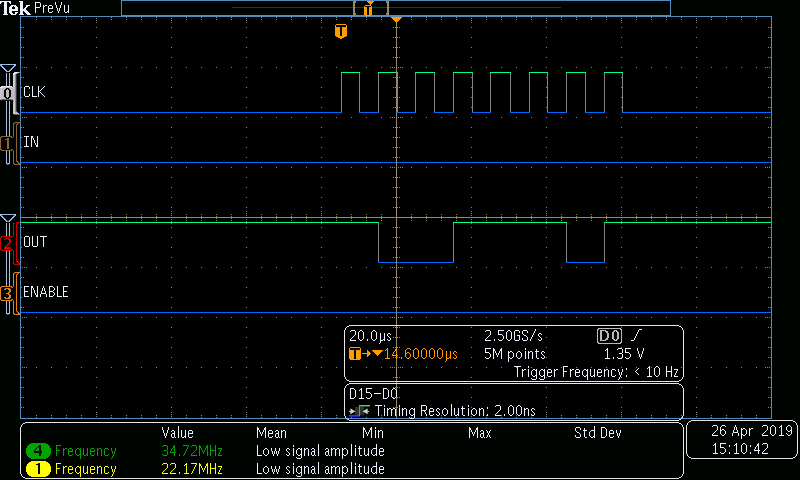

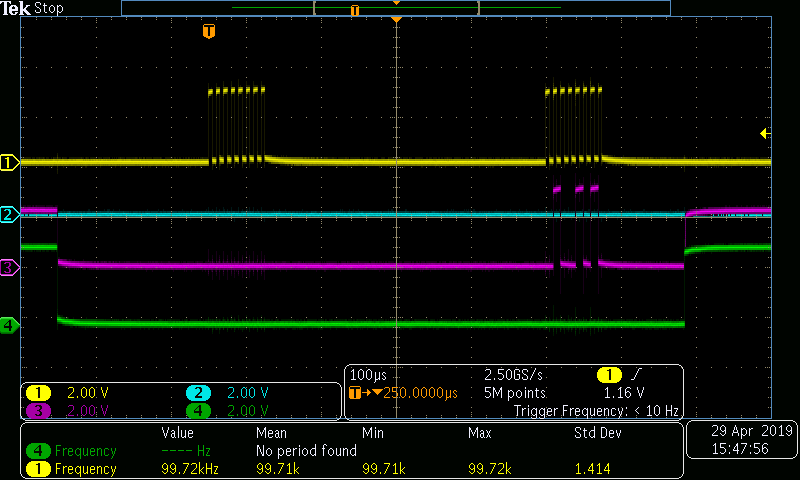

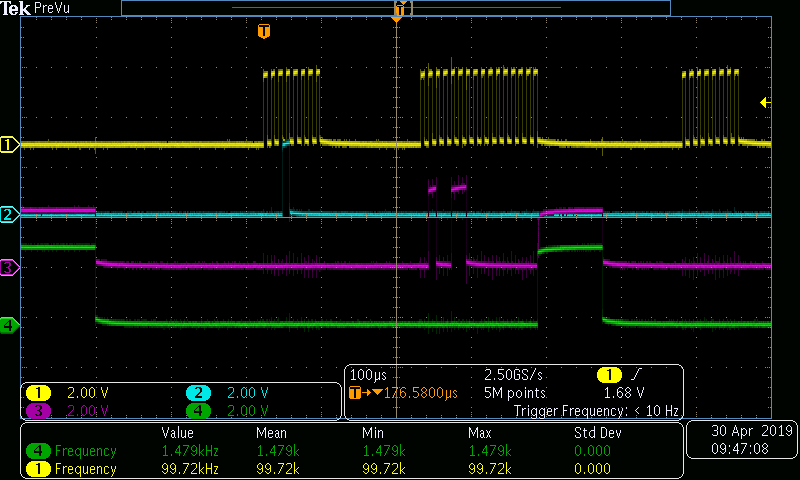

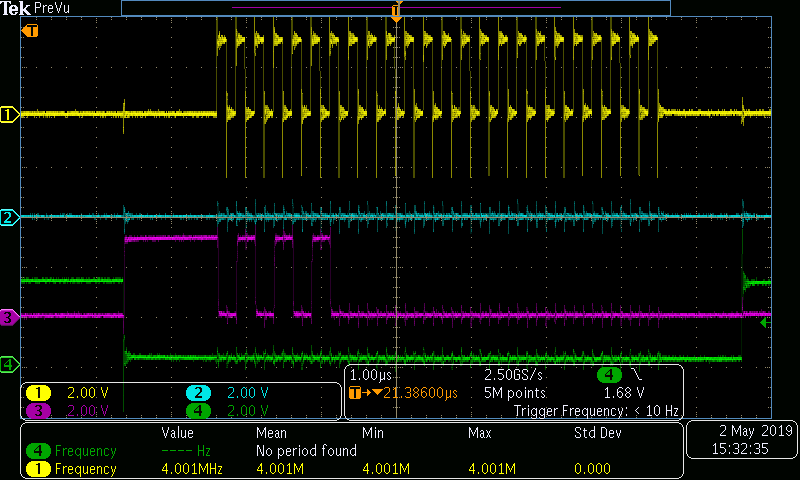

Please see images attached. (IN is MOSI, OUT is MISO)

([0x8, 0x0, 0xAA])

([0x10, 0x0, 0x0])

Read (Data changing on rising edge of clock)

Thank you!

Nik