Other Parts Discussed in Thread: TSW14J57EVM

Hi TI,

We are using ADC12DJ3200 in our project.

ADC12DJ3200 will be interfaced with virtex-7 XC7VX485T FPGA.

We have two questions:

1. Common mode voltage for timestamp input in ADC12DJ3200 datasheet is 0.3v typical.

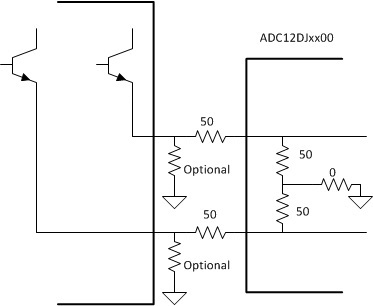

We will be connecting the timestamp inputs of ADC12DJ3200 to virtex-7 FPGA using LVDS standard in FPGA.

Now the common mode for LVDS output of FPGA is 1.25v.

So, do we need to AC couple the timestamp inputs and provide the necessary common mode for timestamp inputs using pull up and pull down resistors on timestamp inputs?

And if pull up resistors are required , which power supply should we use (1.9v analog, 1.1v analog, 1.1v digital) for pull ups?

2. We are using only balun (BAL-0009SMG) for input signal to ADC inputs. Do we also need to use capacitor between SMA connector and BALUN?

Thanks,

Lalit