Other Parts Discussed in Thread: THS4551,

Hi,

Thanks again for your help with our previous questions regarding ADS127L01.

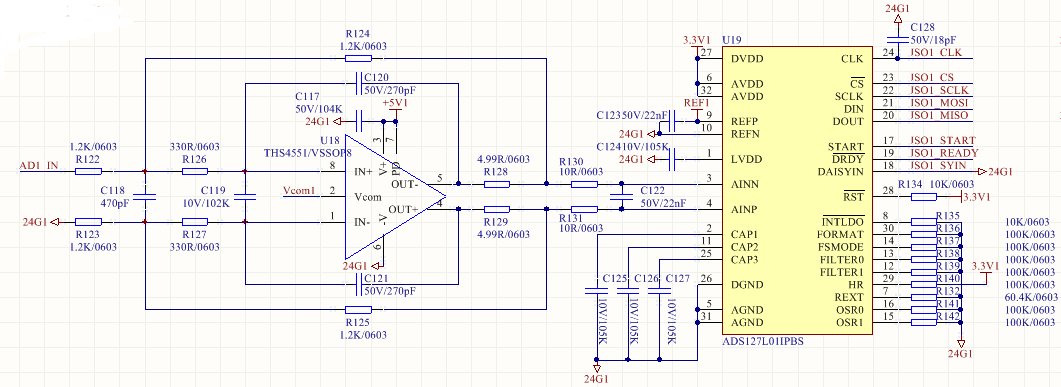

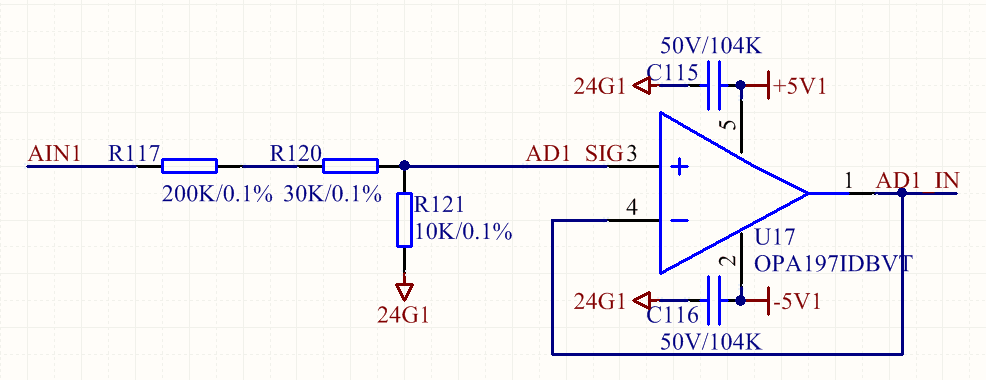

We now able to get digital data from the ADC. The ADC is operating at High Power Mode, using wideband 2 filter(0.45-0.55 Fdata). The AD is sampling constantly at 128kHz. We are using the recommended design with THS4551.

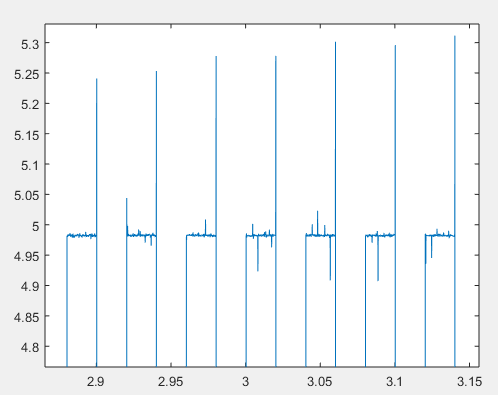

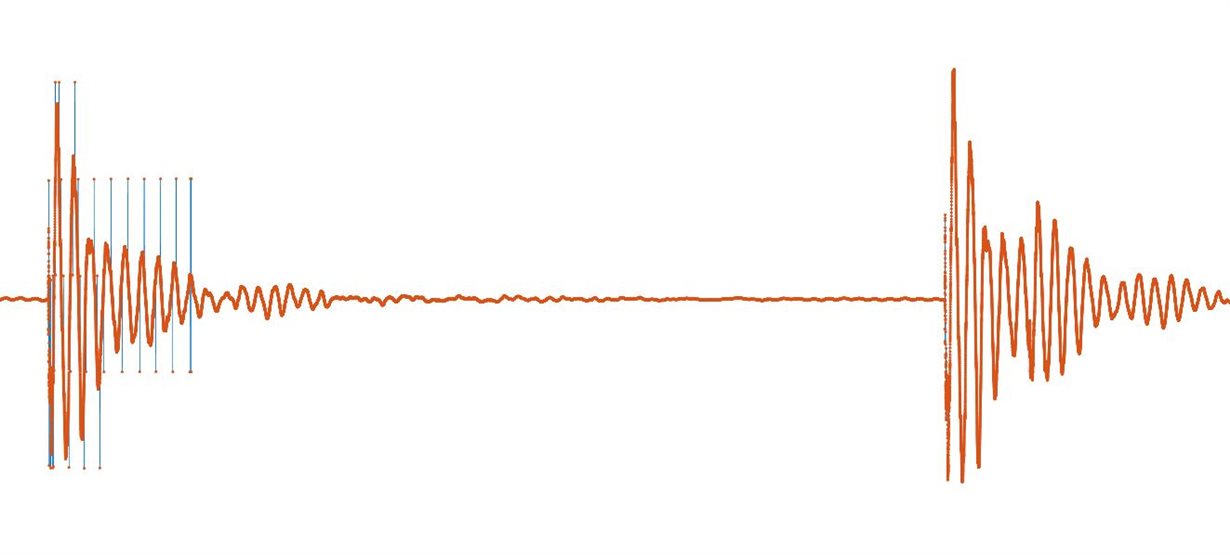

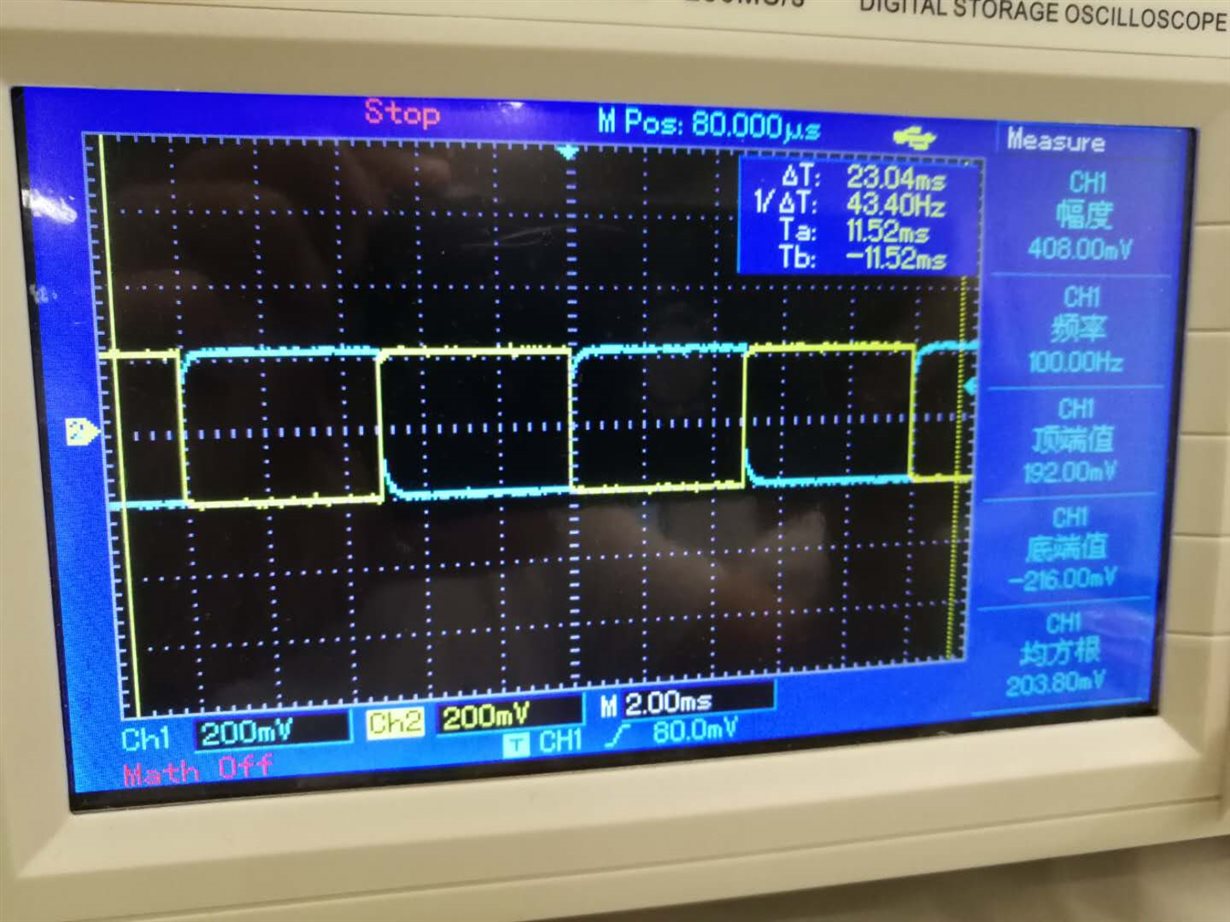

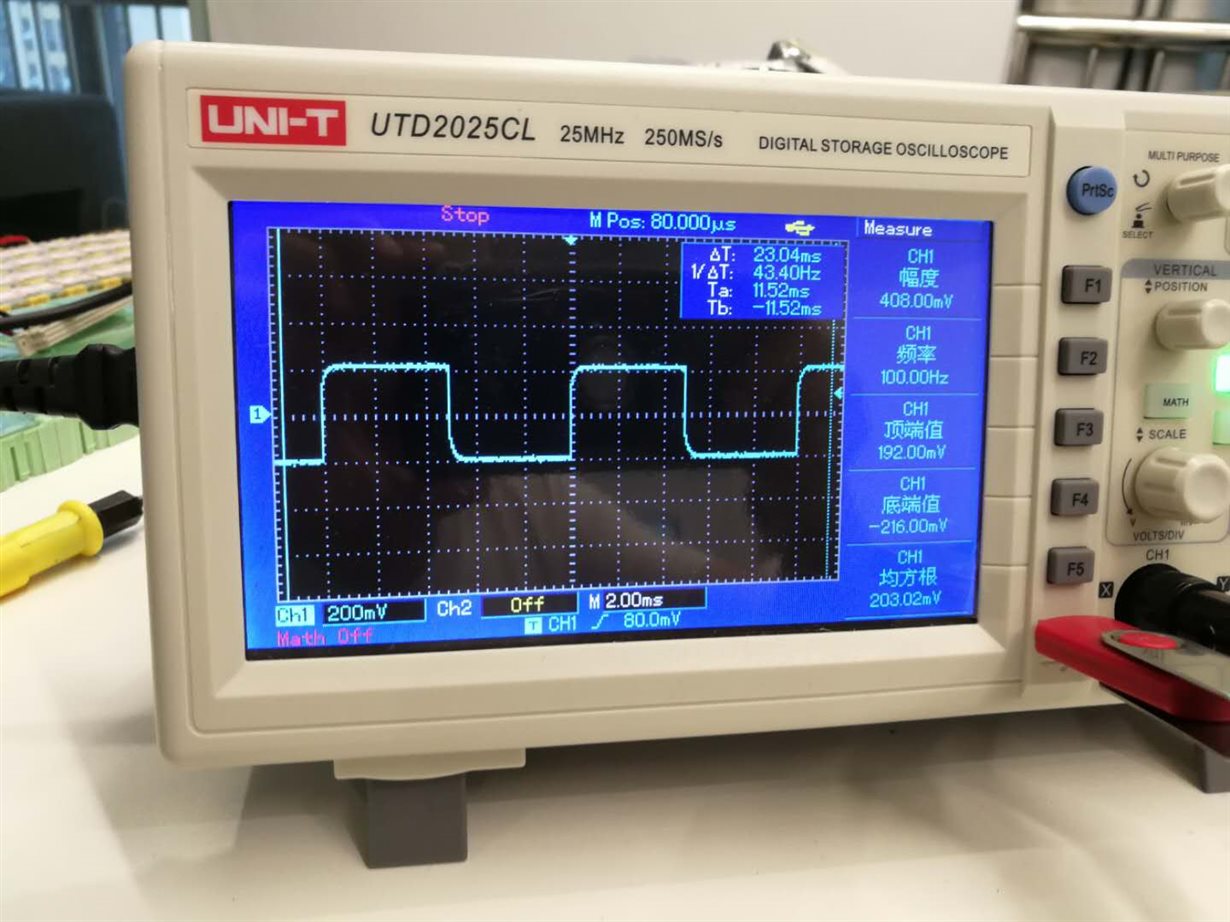

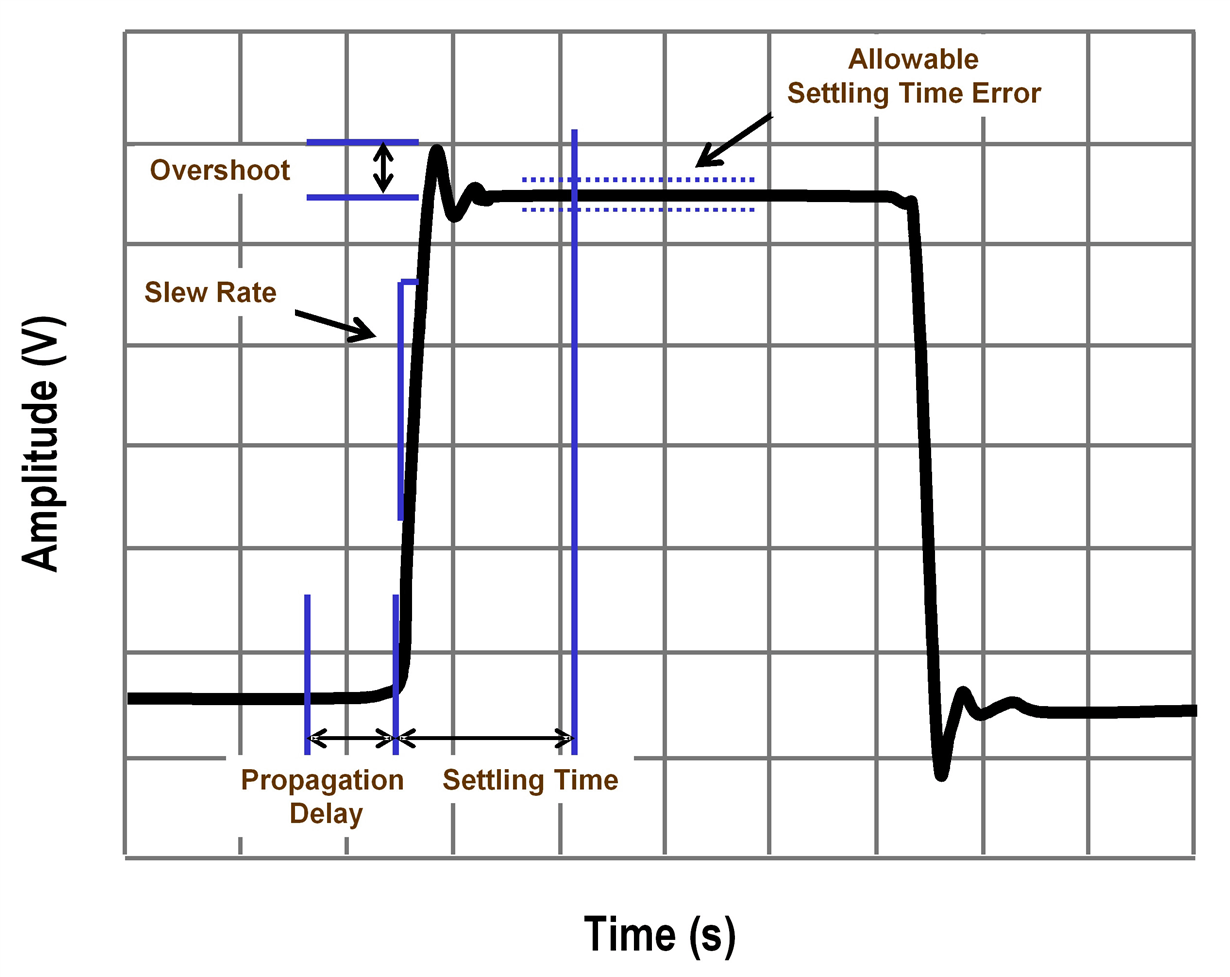

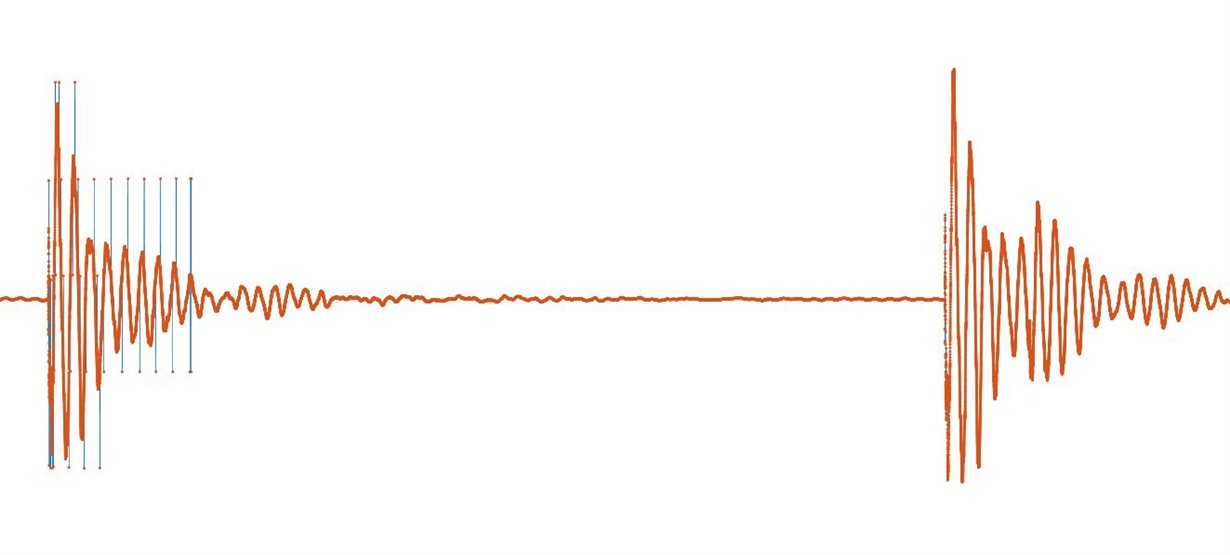

However, we observed unusual spikes in nearly all the tests. it is usually fine with sine wave input when the signal does not change abruptly, but with square wave and pules input, the spikes happens a lot. it seems that the AD need time to settle done. The AD connects to a xilinx Spartan 6 FPGA. We have ruled out the FPGA issue as well as the analog circuit issue before the ADC.

Any clue on what the problem might be? how do we solve the problem.

Thank you

Ben