. We are interested in your DAC7551-Q1. We want to use SPI interface to access it. But we have a question about its Serial Write Operation Timing.

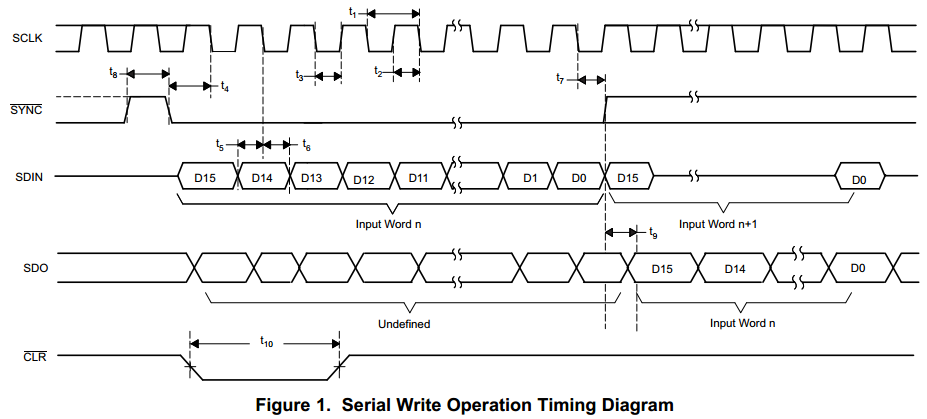

- The datasheet says that the t7 (SCLK falling edge to SYNC rising edge time) should not exceed (t1 – 10 ns) to latch the correct data. This requirement seems not to be a normal requirement in the SPI protocol. From my perspective, t7 is a hold time so it should has the minimum instead of the maximum. If we write 16 bits data to the DAC only once, and then SCLK keeps high, can the t7 exceed (t1 – 10 ns) in this senario?