Other Parts Discussed in Thread: LMK04828

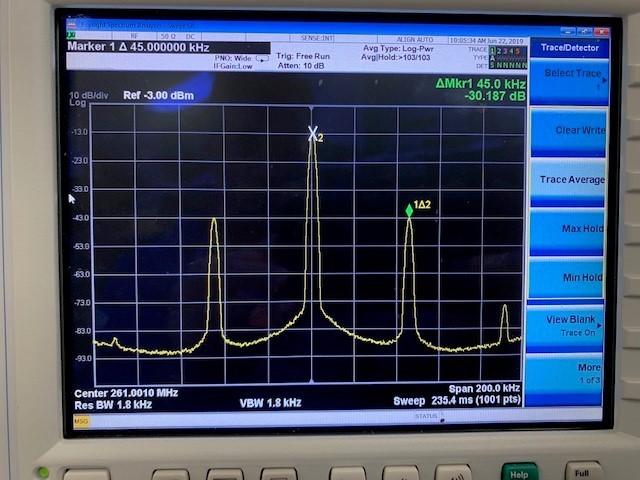

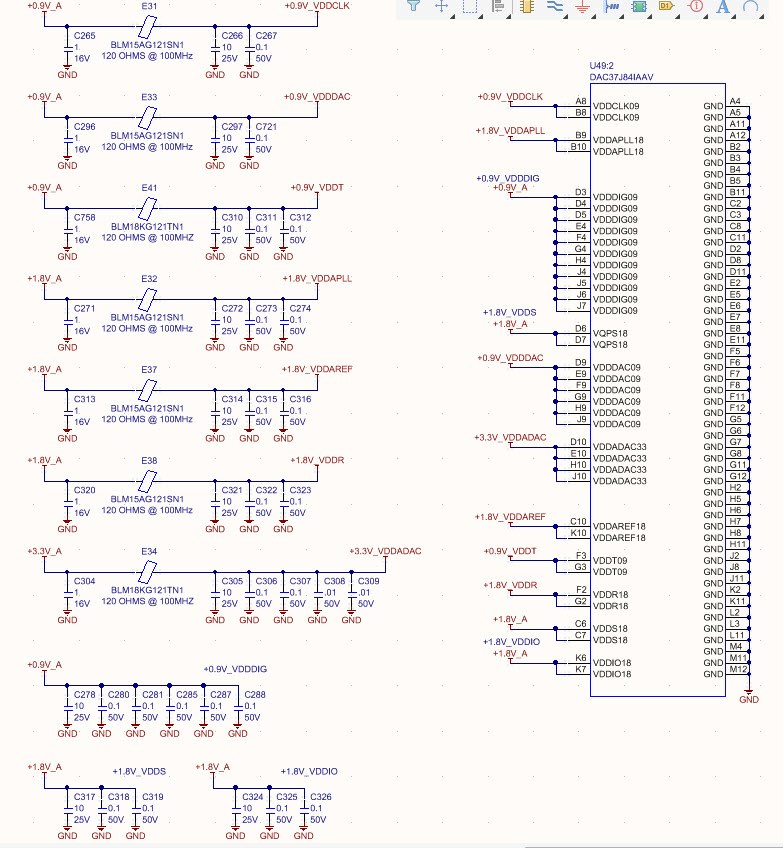

Currently our DAC is setup to use the CLK PLL to generate a 1.2GHz sample clock from a 600MHz input clock. At room temperature the DAC appears to put out a normal tone, however, once we start dropping the temperature in the chamber spurs at a 45KHz offest (and harmonics) start to appear and grow in amplitude. The images attached is at -39C. If we do not use the CLK PLL and sample with just our incoming 600MHz clock, there are no spurs. It appears that the CLK PLL has some instability. We tried lowering the charge pump current from 1mA to 500uA, but did not observe any change. The VCO is set to 4.8GHz, Prescaler at 4, M=2, N=1.

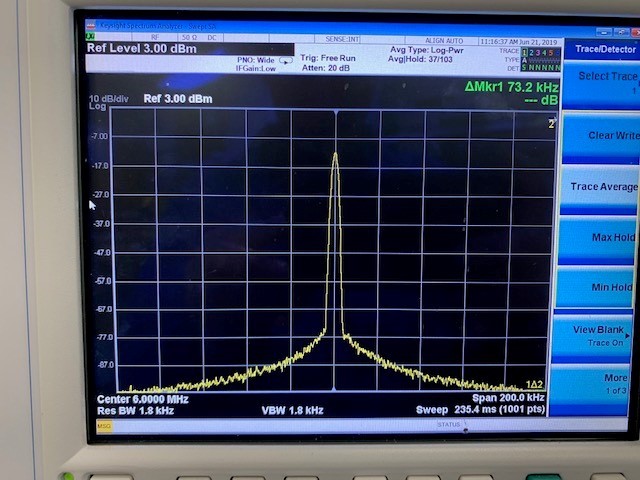

No Clock PLL, tone at 6MHz

With Clock PLL, tone at 261MHz ( spurs will also show up with a 6MHz tone just the same).