Dear Sir

I had developed a board with TI ADC12D1800RFIUT, FPGA and ZBT Cypress SRAM.

In the Hardware, Each ADC/SRAM is powered up by a separate LDO.

While the FPGA VCCO/AUX Core Voltages are powered up by DC-DC Regulators.

Issue Experienced

-----------------

1.) When the FPGA is doing a SRAM read operation, I had experienced ADC spurious.

2.) When the FPGA is doing a write SRAM operation, it does not experience much spurious.

3.) When the FPGA is not doing any read/write SRAM operation, the ADC performance is good.

What I had done

-----------------

a.) I had tried to reduce the SRAM Clock, the spurious will just follow the harmonics. I had also tried to reduce the data toggling rate from 100% to 25%, the spurious will spread across the spectrum.

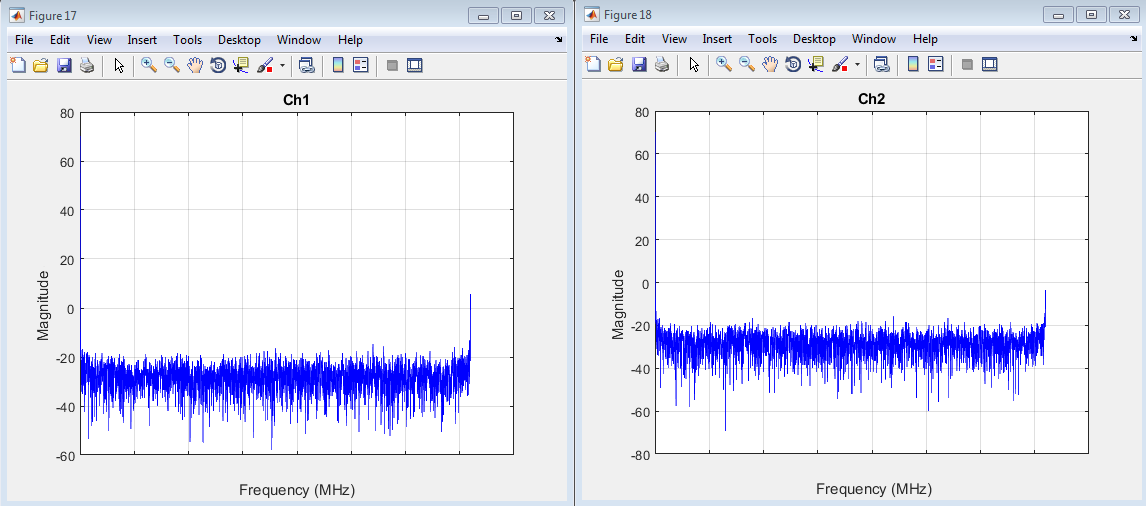

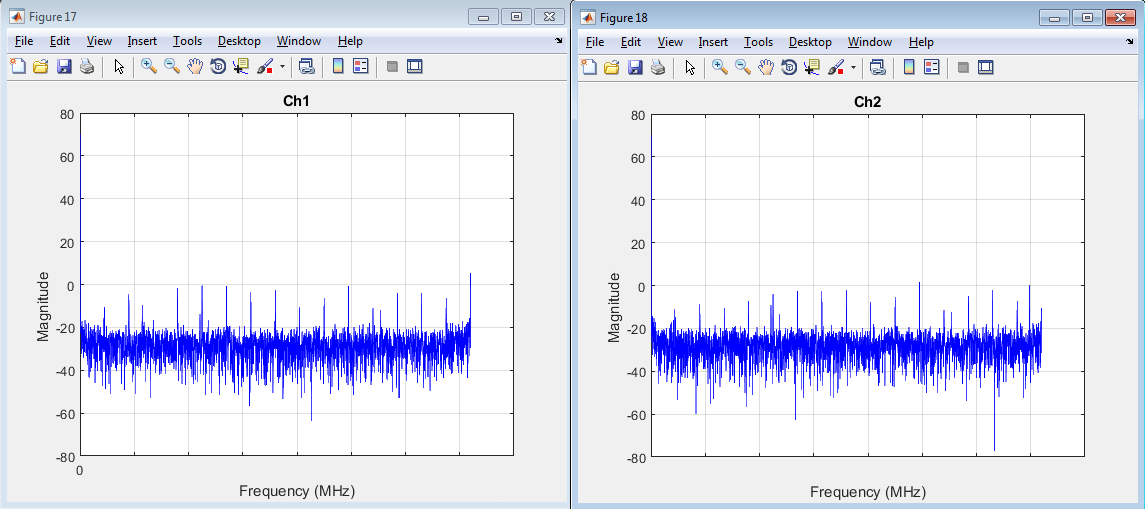

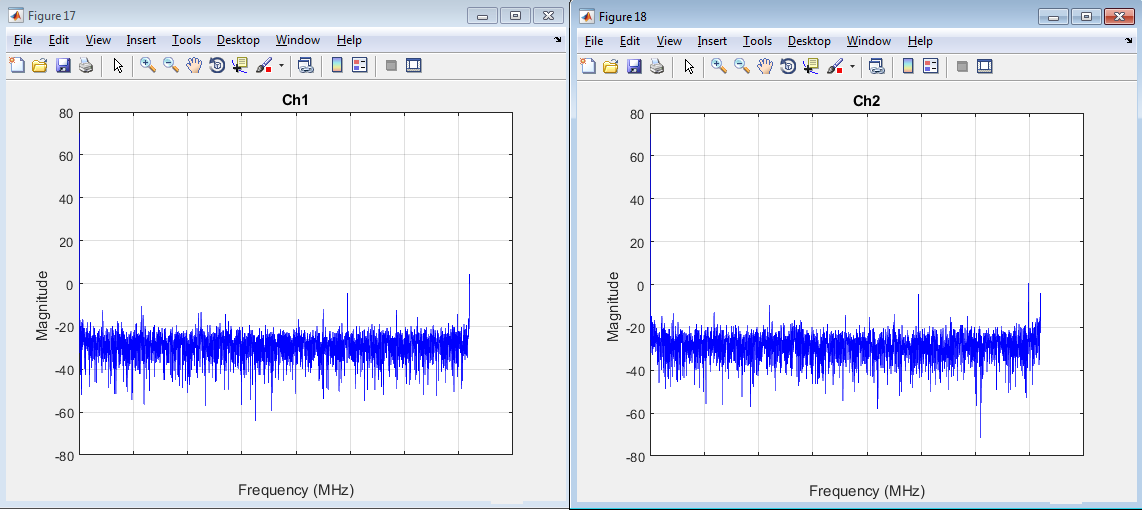

Attached the ADC Spectrum for your reference. The ADC Analog Input is terminated to 50ohms.

I had also tried the following method

b.) Activate the ADC Test Pattern while doing a SRAM read operation, the ADC test pattern is verified to be correct. This means that there isn't any digital crosstalk interference between the SRAM and ADC.

I had read the datasheet and TI recommend that the AGND/DGND does not require any isolation and can be connected together.

Do anyone have any solution/recommendation on the above issue?

Hope to receive your reply soon

Warmest Regards,

Alex

Capture ADC Data while SRAM in IDLE state (No SRAM read/Write)

Capture ADC Data while Read SRAM continuously

Capture ADC Data while Write SRAM continuously