Part Number: ADS1191

Other Parts Discussed in Thread: SN74LVC3G17, SN74LV1T34, ADS1292, ADS1298, ADS1294

Hello,

I have a question again...

In the following I wanted to concentrate on the ADS1191 first of all.

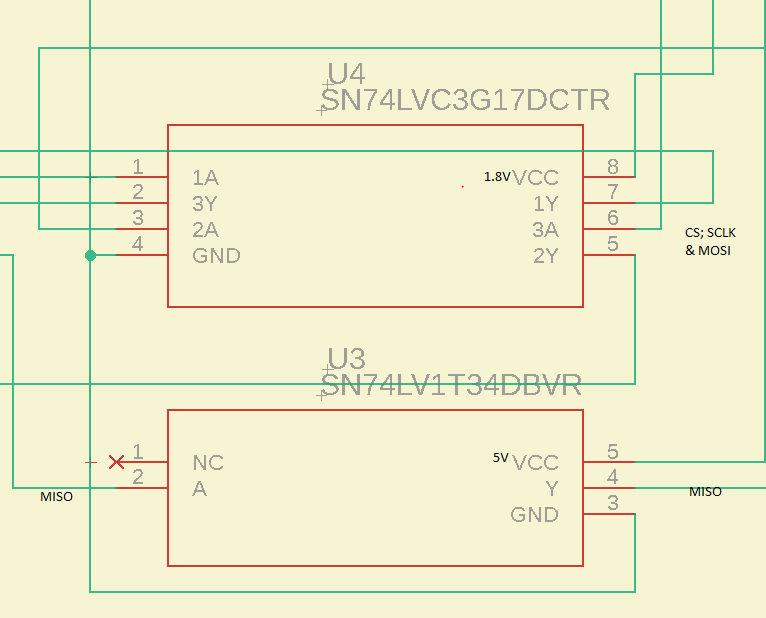

I built the following circuit:AVDD = 3.3V, DVDD = 1.8V

When I connect the circuit, I would expect the DRDY to start pulsing as soon as I set "Start" to High or change its status as soon as I send a command.

However, the line remains low all the time.

Can I somehow measure the full functionality of my chip or is the circuit so usable at all?

To convert my 5V digital inputs I use the SN74LVC3G17 and SN74LV1T34 as follows:

Many thanks in advance!

Hendrik