Other Parts Discussed in Thread: MSP430F249,

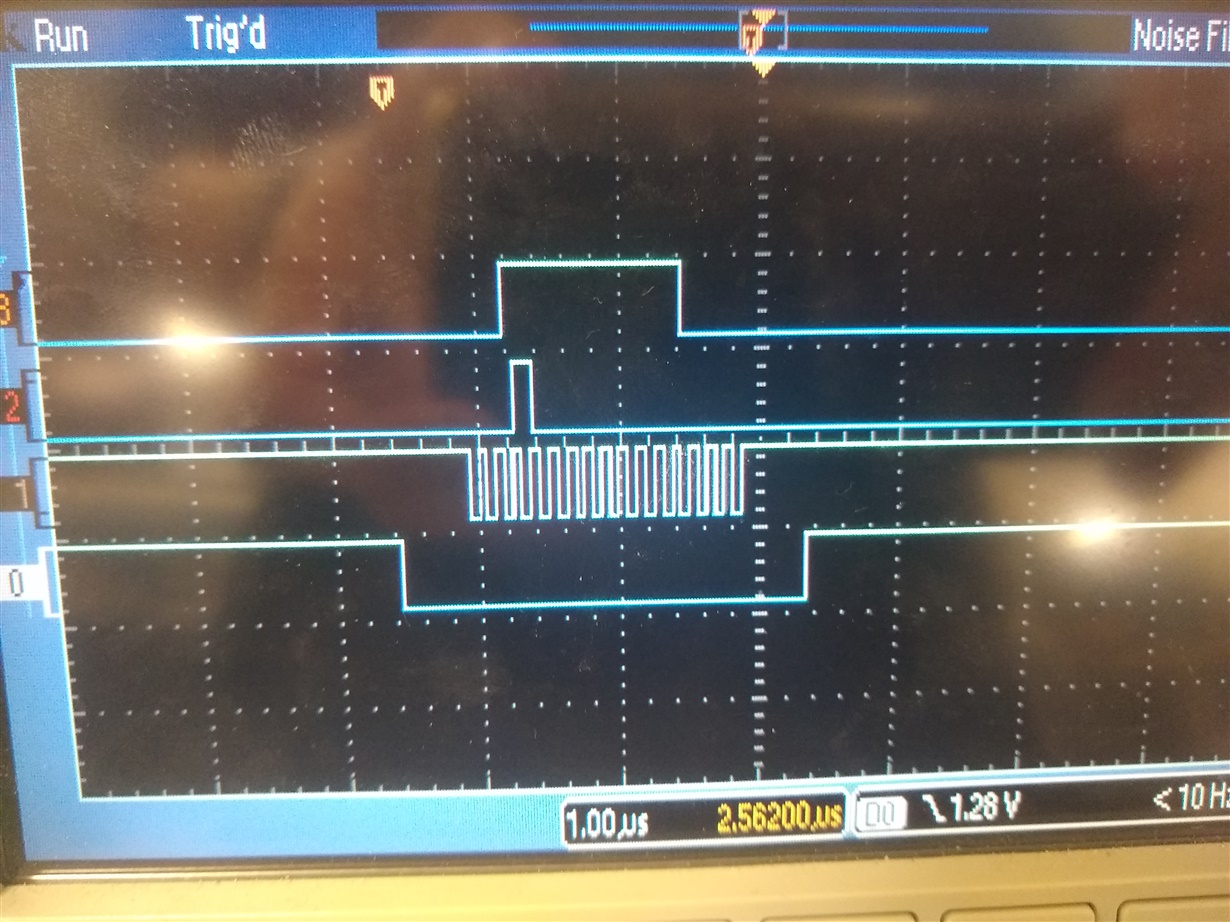

I'm using an ADS7853 with an MSP430F249, and I seem to get an extra frame when I talk to it. I am running the ADS7853 in 16-CLK Dual SDO Mode with 16 CLK cycles per frame, however after I run the first frame and receive my data I get data on the second 16 CLK frame. Without this second frame that block of data will move over to the first frame and I get no data back. Is this second frame necessary? From reading the data sheet I was under the impression that you only needed one frame to read the ADC register. I have attached two pictures of my scope; one with the two 16 CLK frames and one with only one frame. Also, the command I am sending the chip is 0001_0000_0000_0000.

Thanks yall