Hello,There

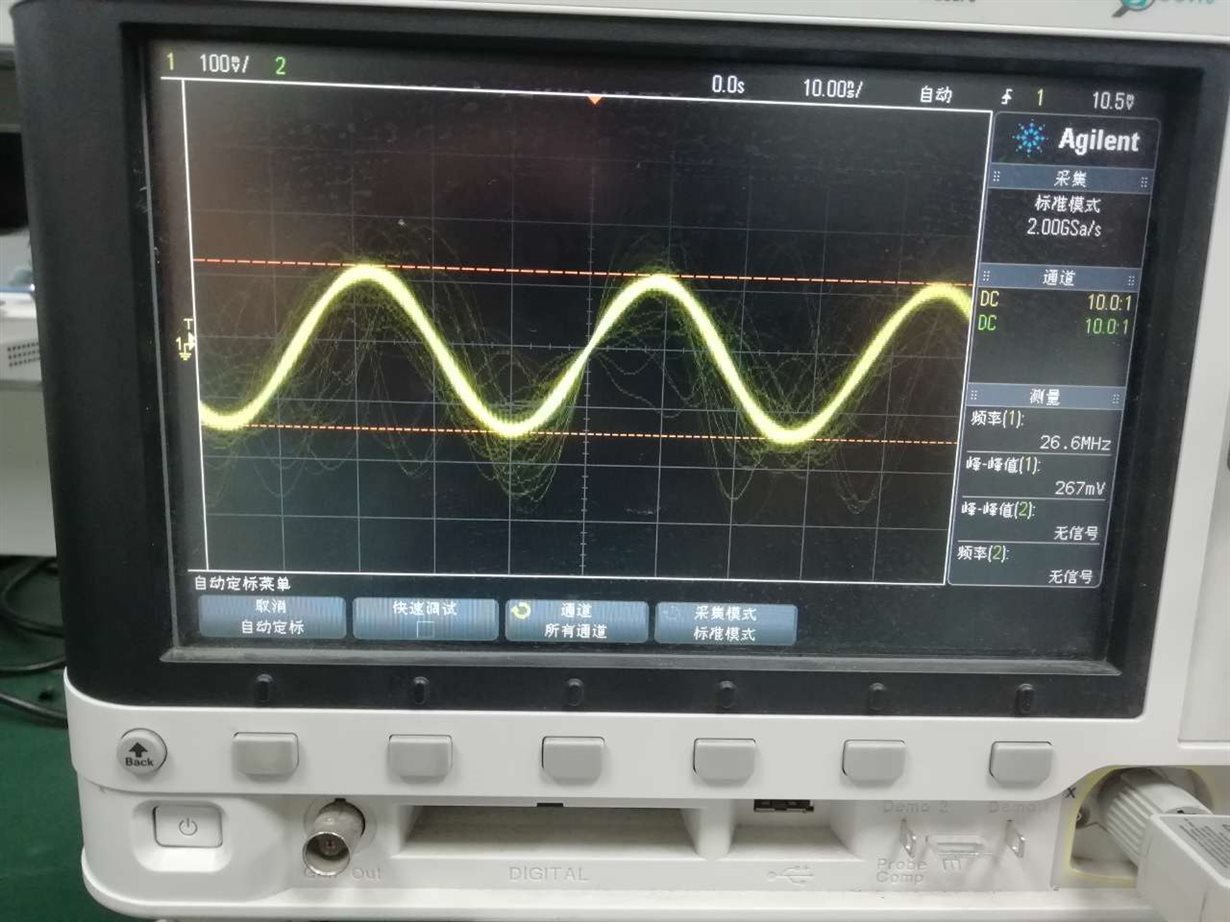

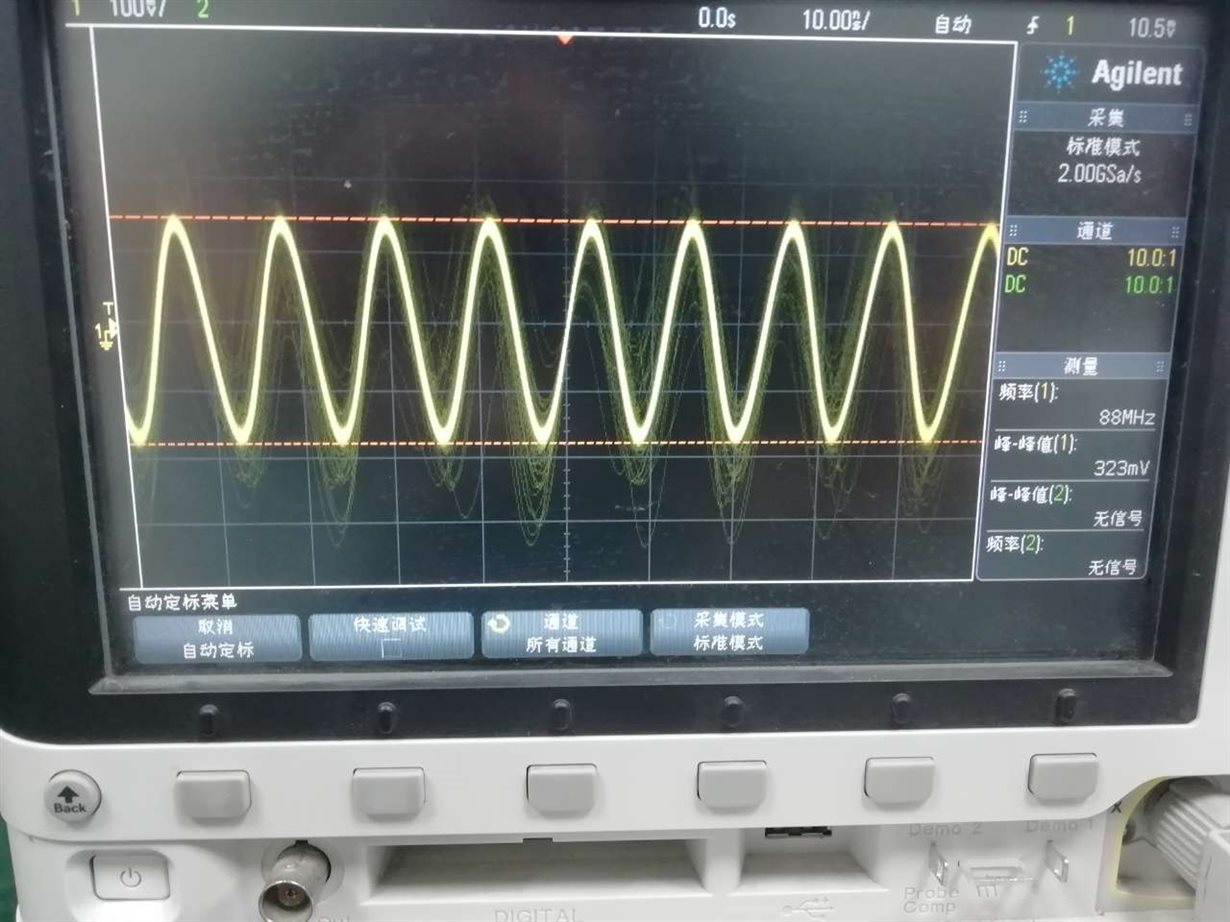

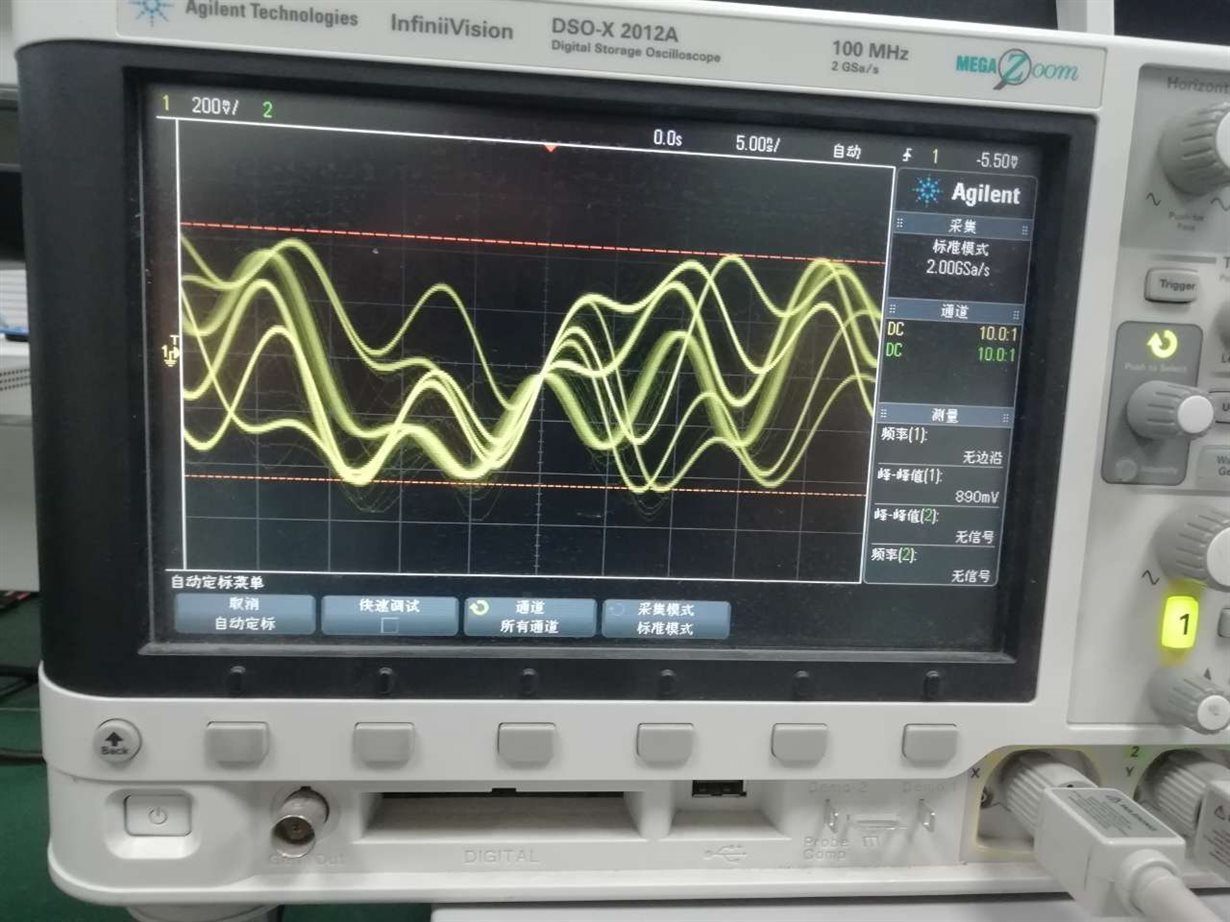

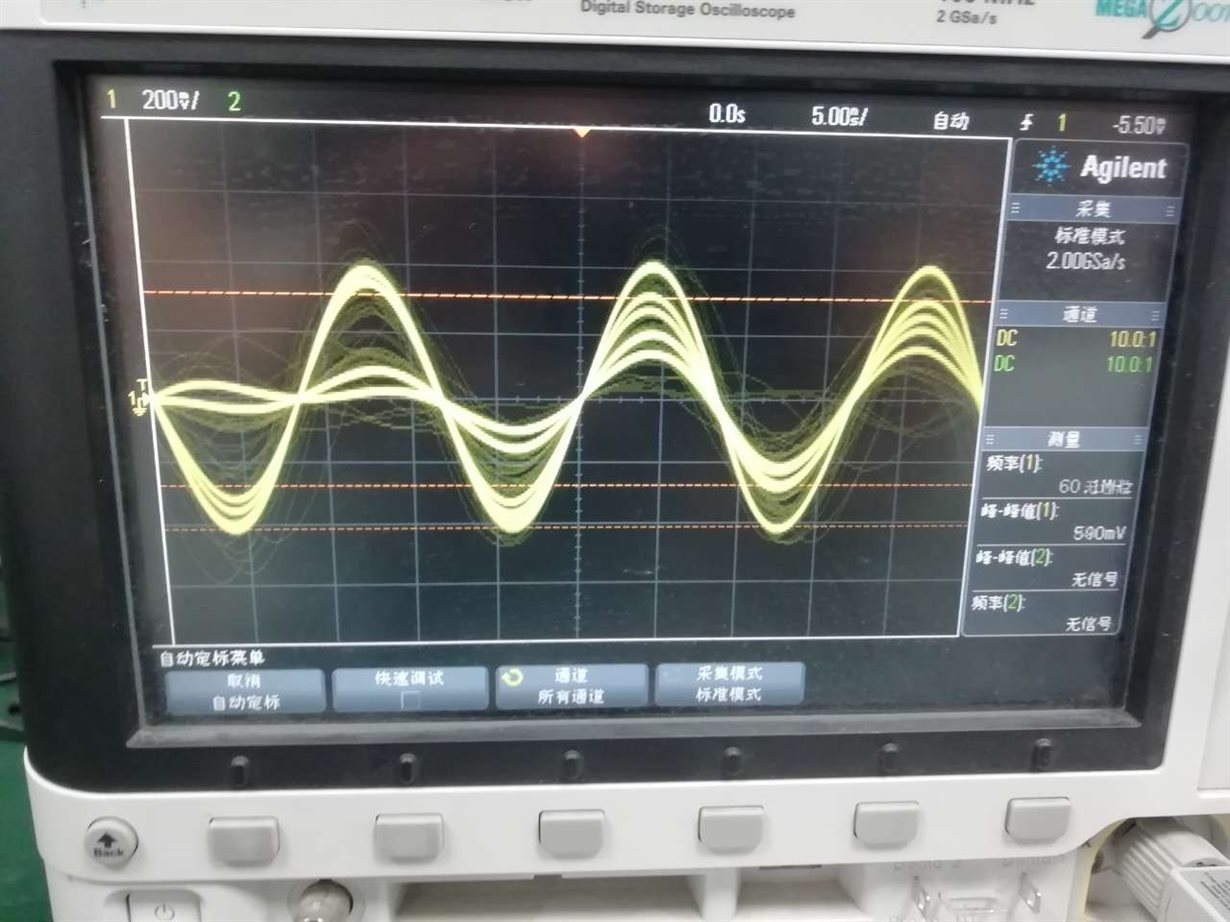

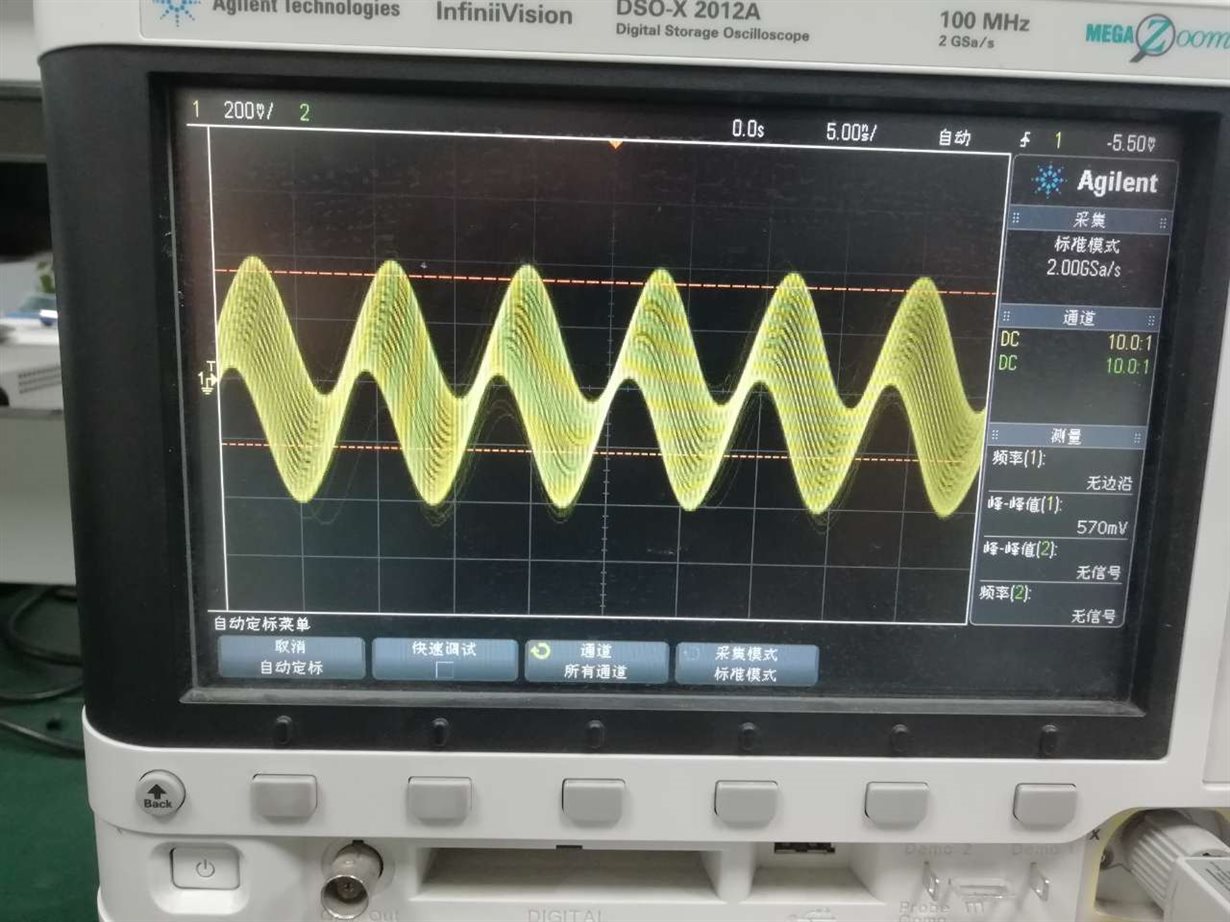

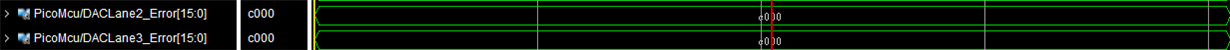

We are now debugging DAC38RF82, In the mode LMFSHD=82121 ,DAC is working good;But,In the mode LMFSHD=22210 DAC report link config, frame alignment errors.

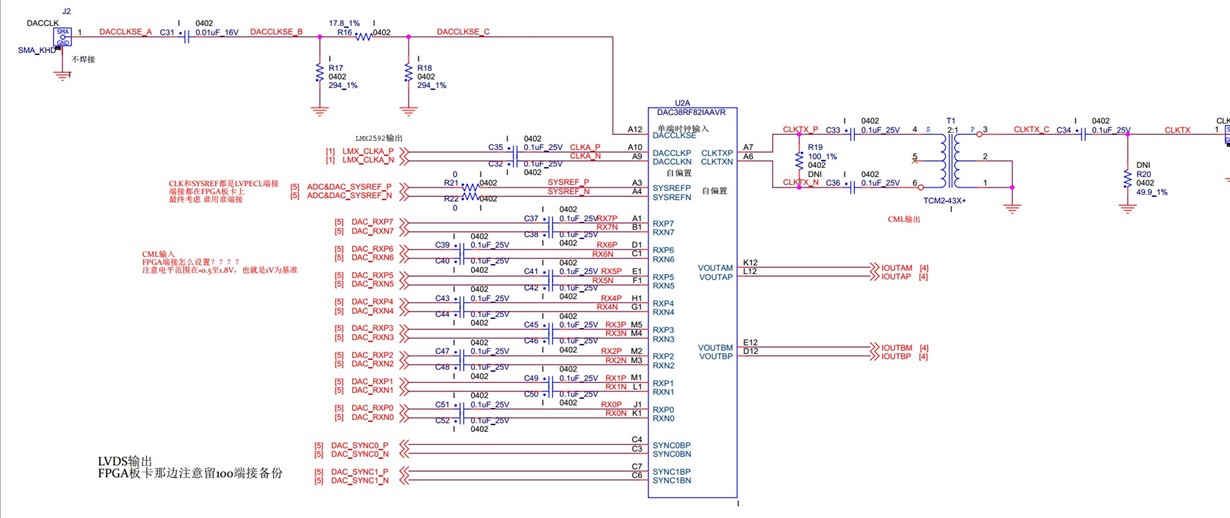

Design details:

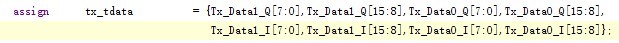

(1)LMFSHD=22210;

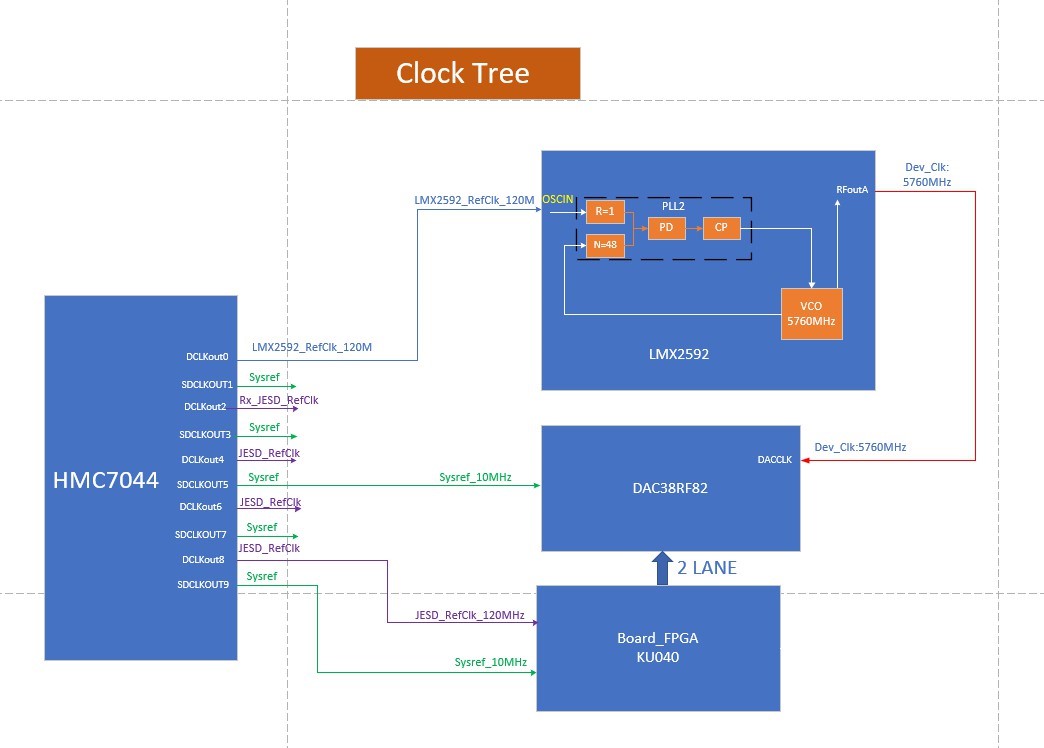

(2)FDac(DACCLK)=5760M,External Diff Clk;

(3).Single DAC(DAC A)

(4) 1 IQ pairs

(5) 2 serdes lanes

(6)Interprolation=24

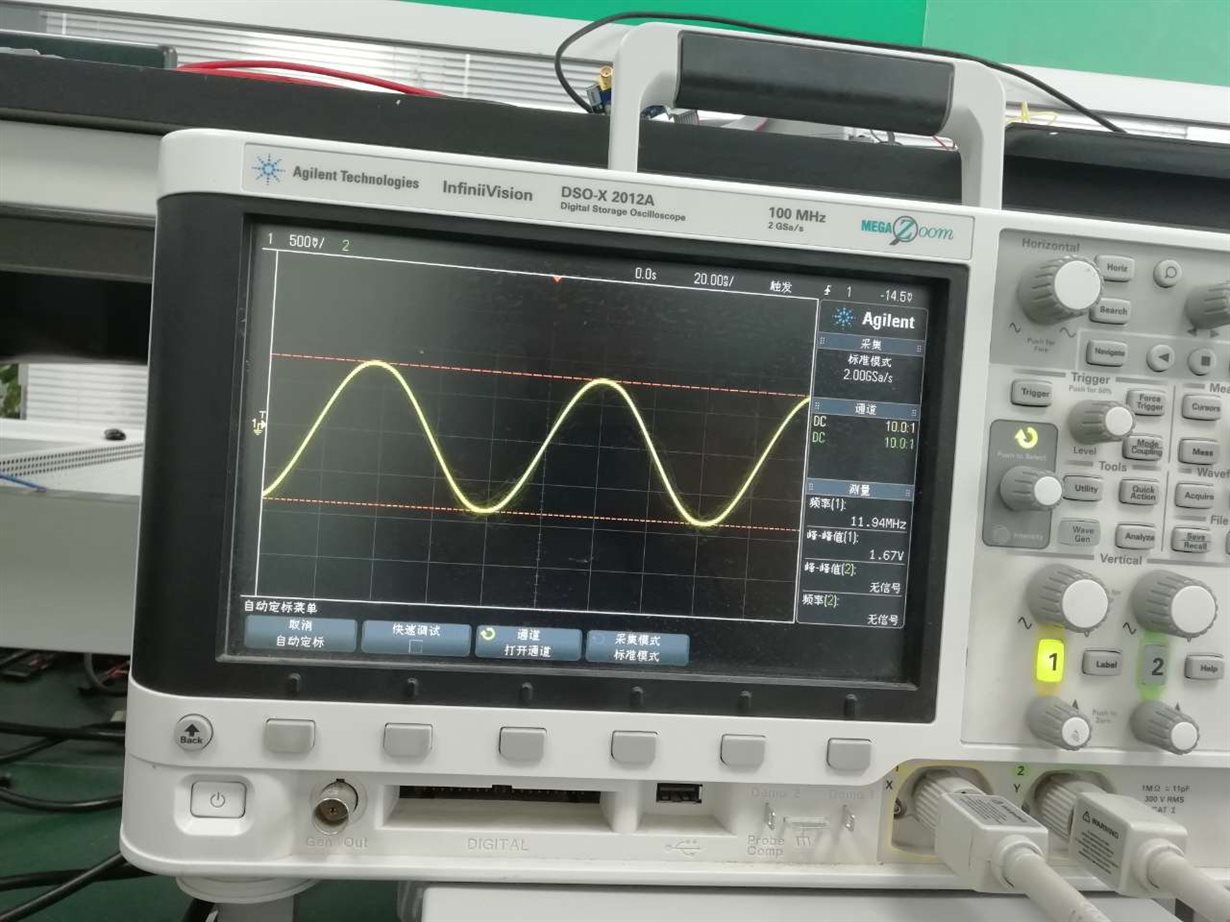

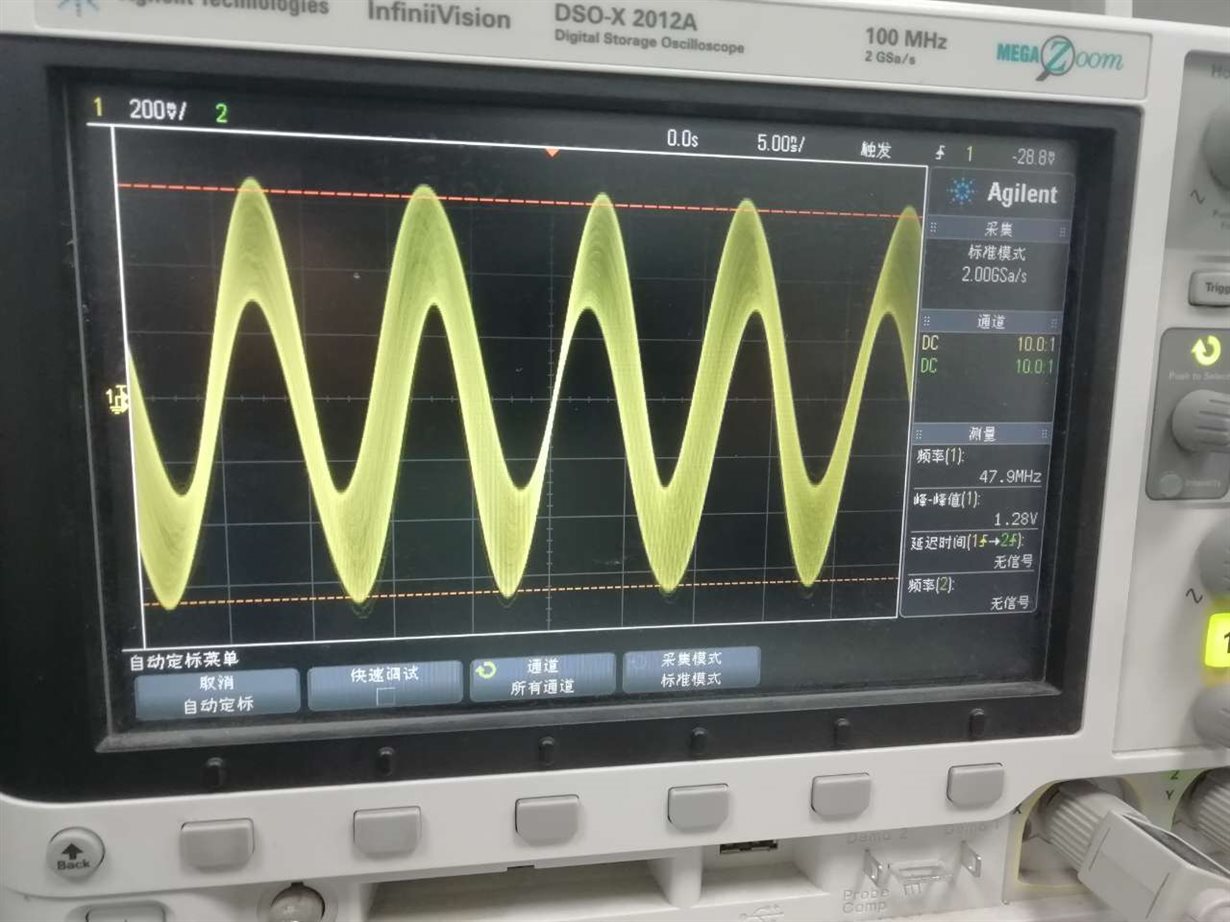

(7)output IF analog signal=1.7GHz

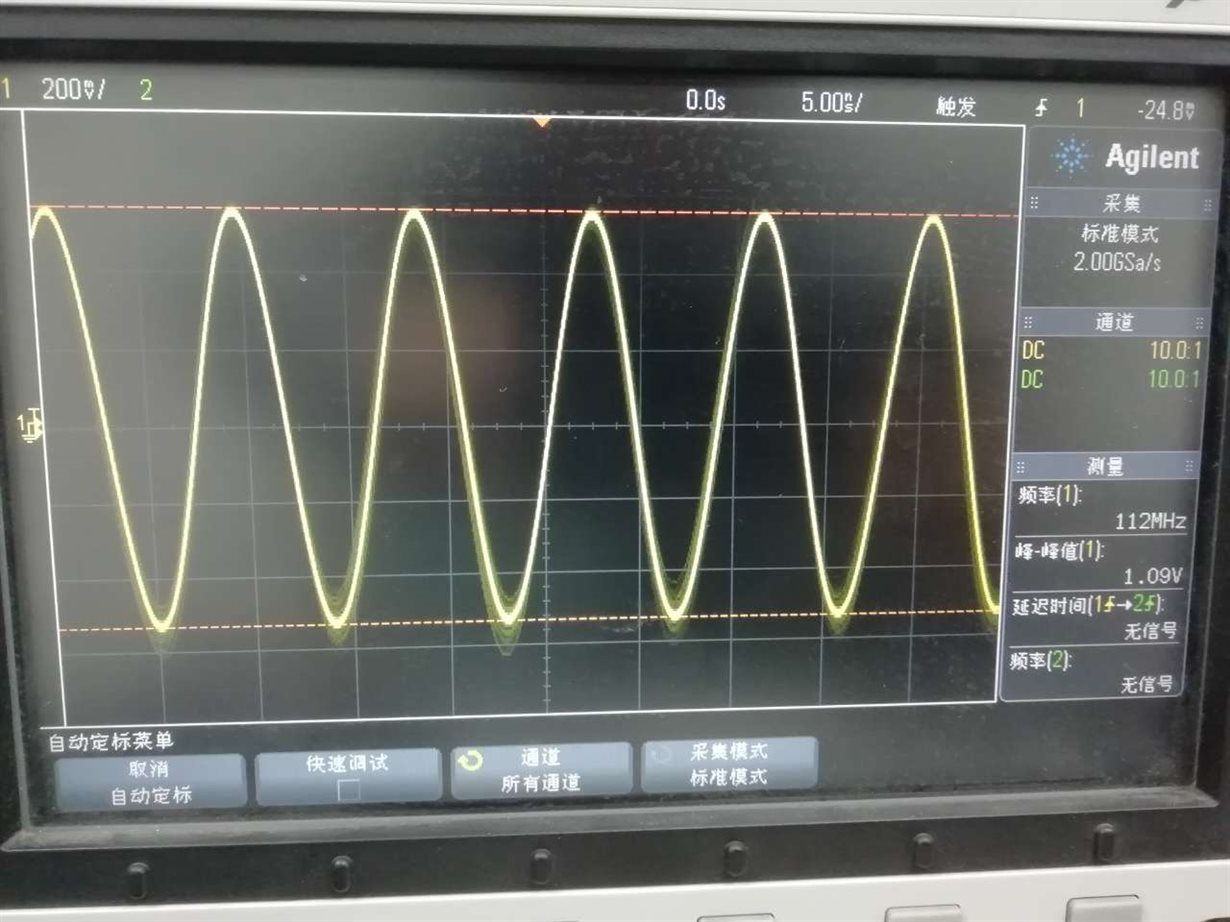

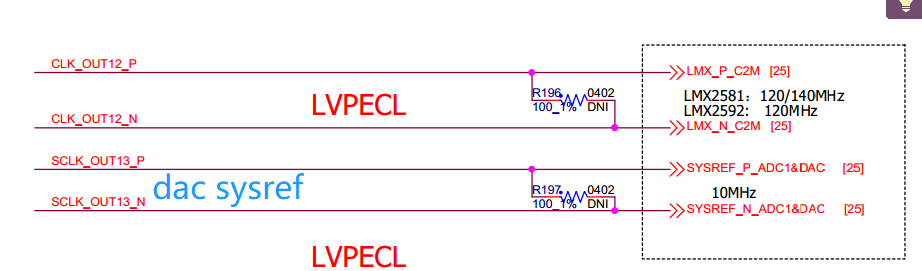

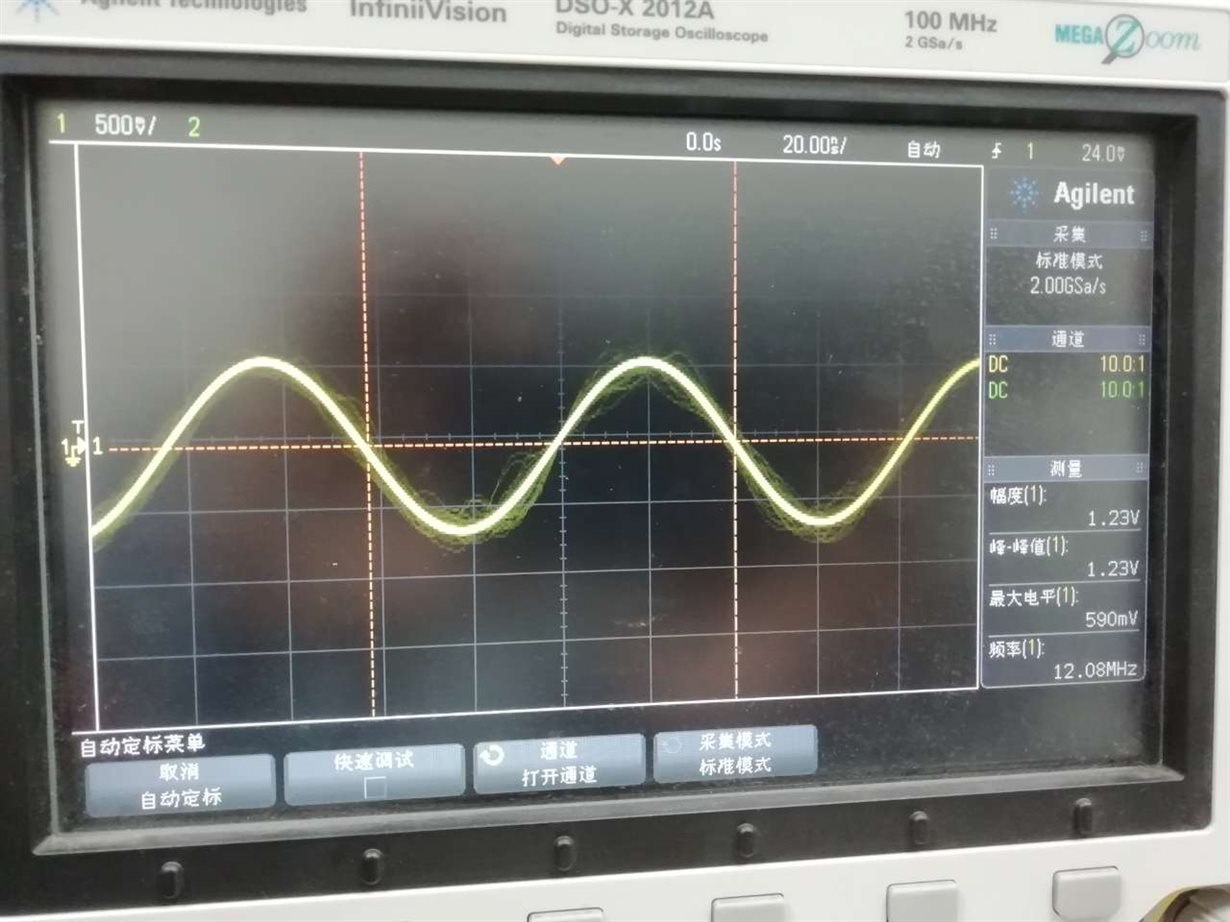

(8)sysref=10MHz

(9)FPGA GTH refclk=120MHz

(11) K=24,RBD=23

QUESTION:

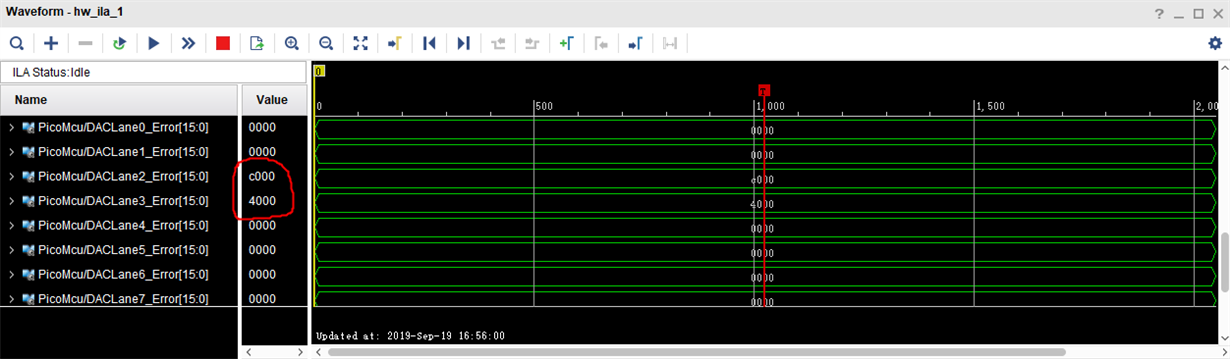

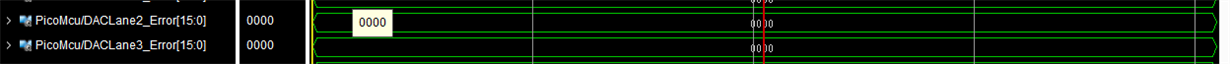

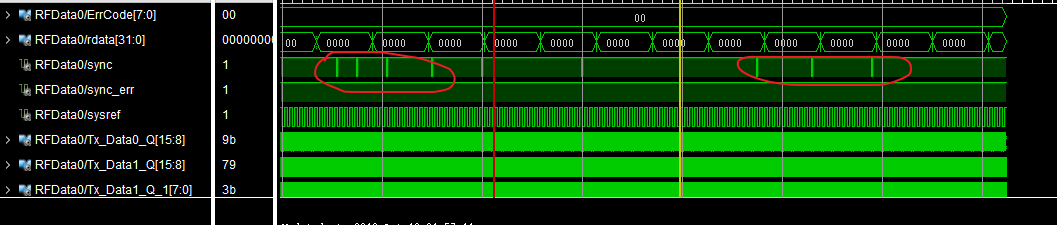

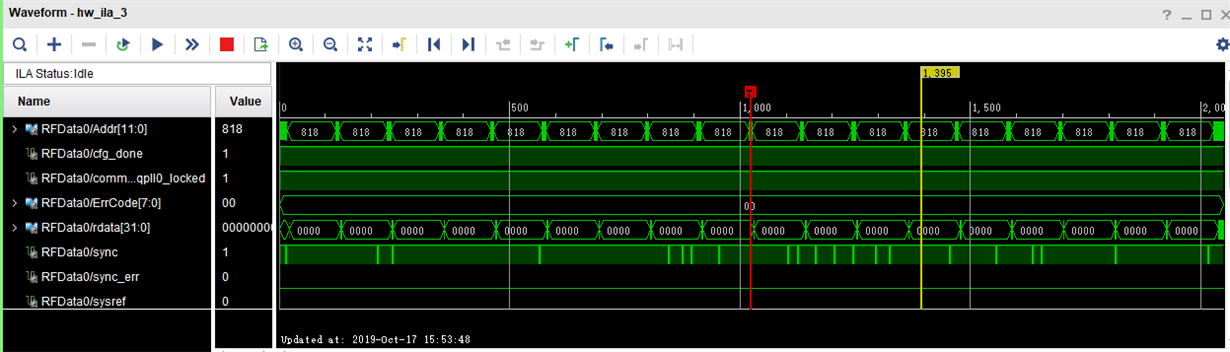

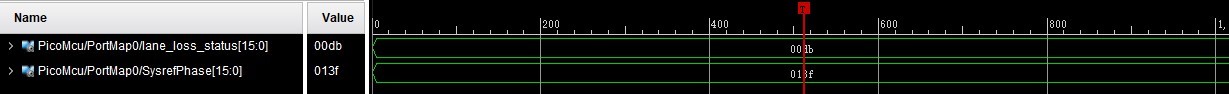

1. We read register 0x66 to 0x67;

(1)register 0x66 is 0x2000;link configuration error

(2)register 0x67 is 0x6000;link config error, frame alignment errors.

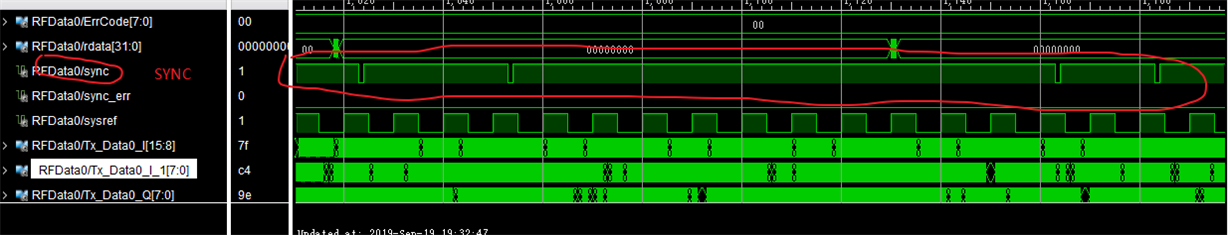

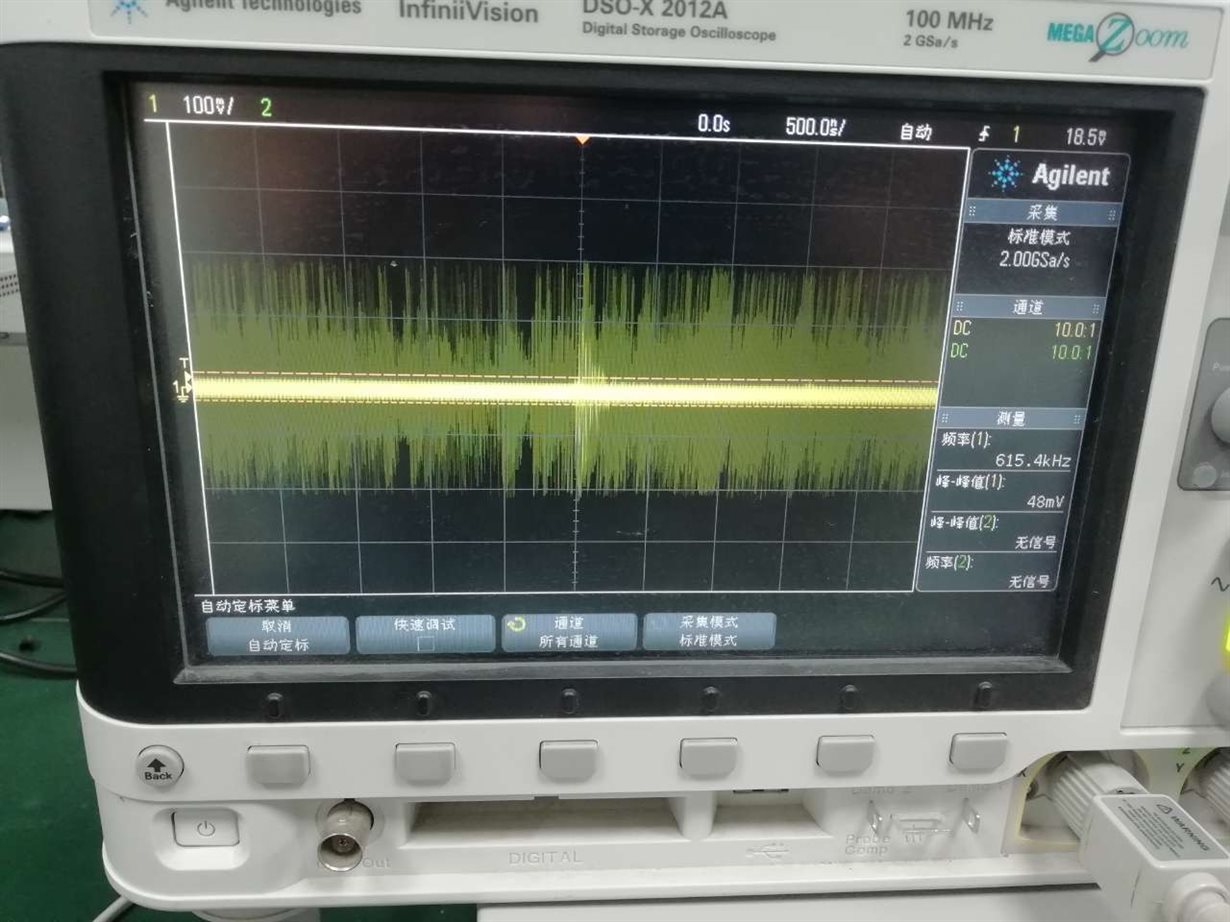

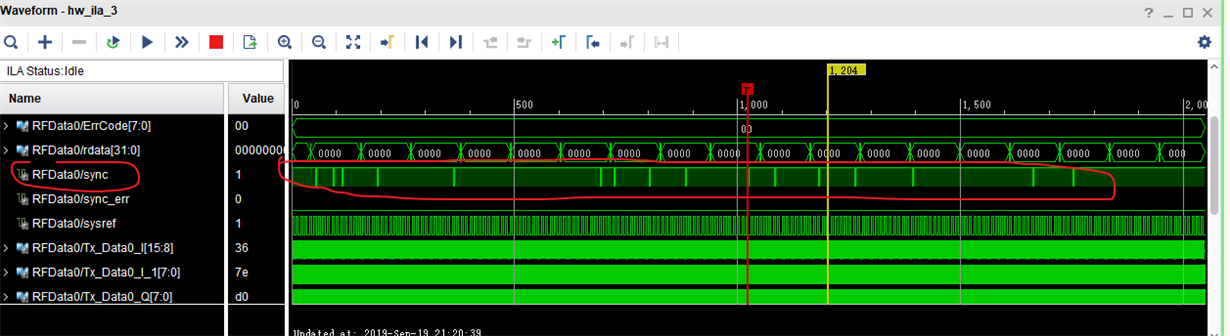

2.there is no data output,Sync always from High to Low

Best Regards,

Wong