Part Number: ADC12D1600

Hi team,

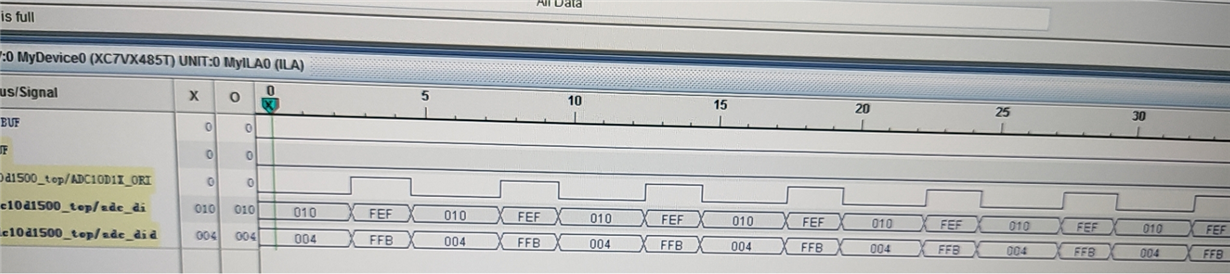

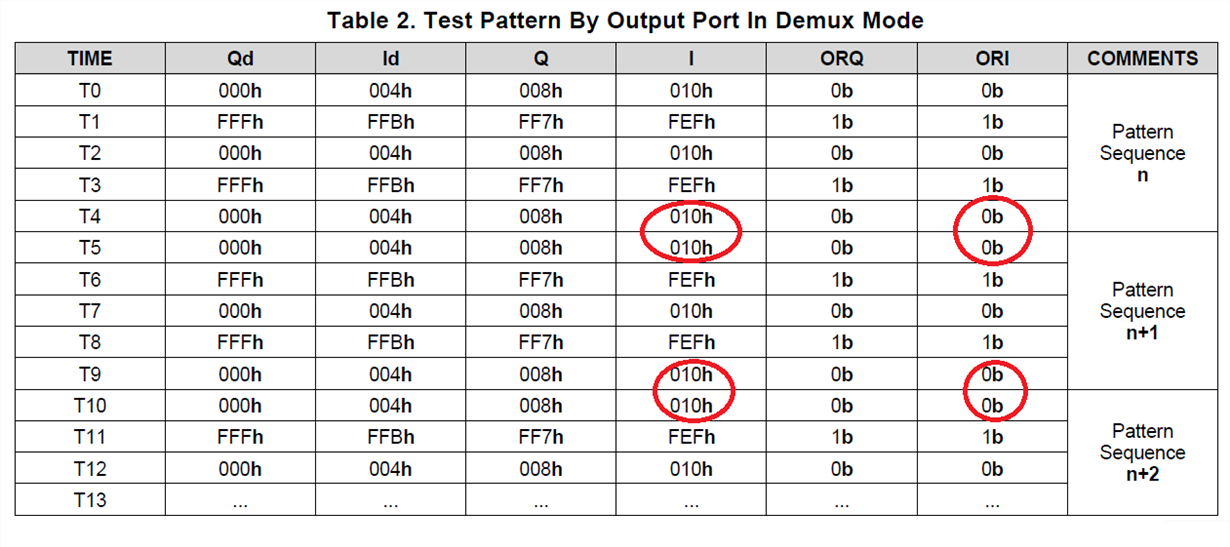

Customers use PIN mode to control ADC12D1600, In Demux Mode, Non-DES Mode, power-on calibration, use test pattern, according to the datasheet description, test pattern will have a continuous 010. Now the data DI captured by customer in the FPGA FEF is two cycles, 010 is three cycles, and 010 does not appear twice the cycle of FEF. The timing constraints meet the requirements. What may be the problem?

Best Regards,

Amy Luo