Hello, We take the 'Vout' value with FPGA, and foud the numerical value sometimes quite different from the reality.

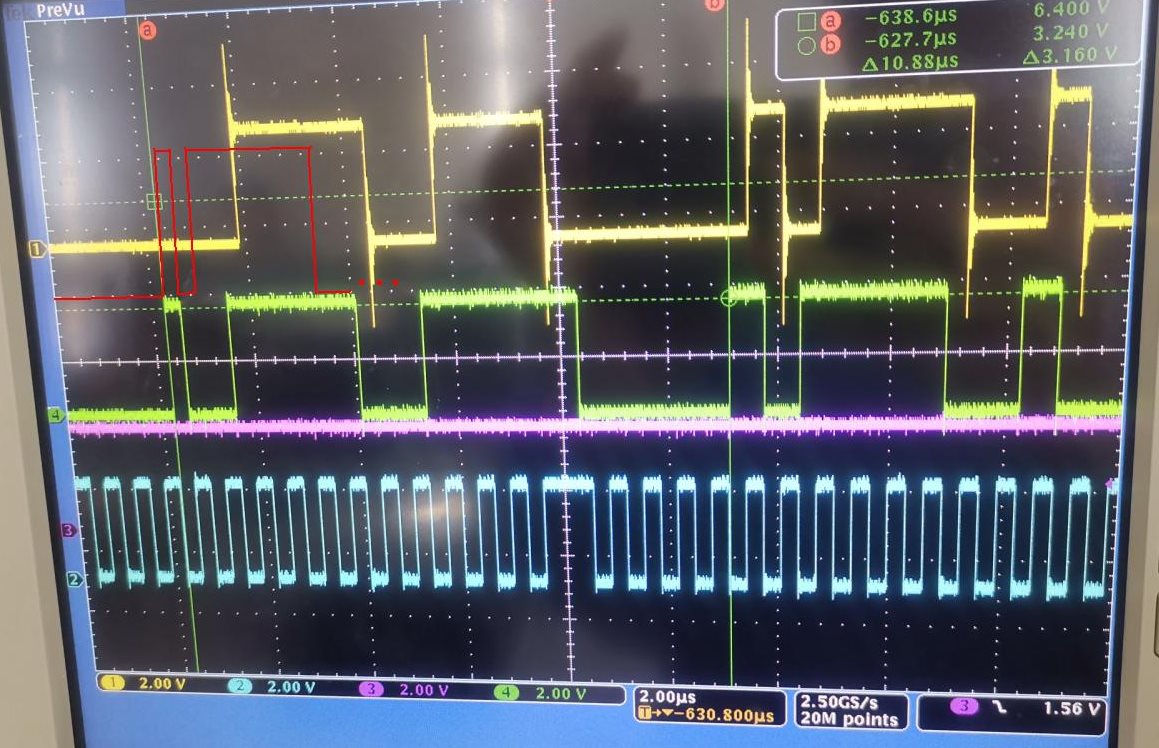

So we captured the waveform with an oscilloscope like this:

In the figure above, from top to bottom: ①Data collected by fpga through SCLK rising edge, ④Dout, ③Don't care(we use it to track strange anomalous value) , ②SCLK

The two green rulers are marked at the beginning of each DOUT. And the sequence starting at ruler B is correct, it should be (10111...), something strange have appeared in the sequence which beginning at the ruler A, some Dout output samples are clocked out on the rising edges of the SCLK

At first, we suspected that the ADC128S102 had caught the falling edge feature by mistake on the rising edge of SCLK, if this is the case, the later wave forms will also move forward(As the red line marked in the picture below), It won't miss the falling edge next to. But the reality is: the high level(1) lasted half a cycle and low level(0) lasted one and a half cycle.

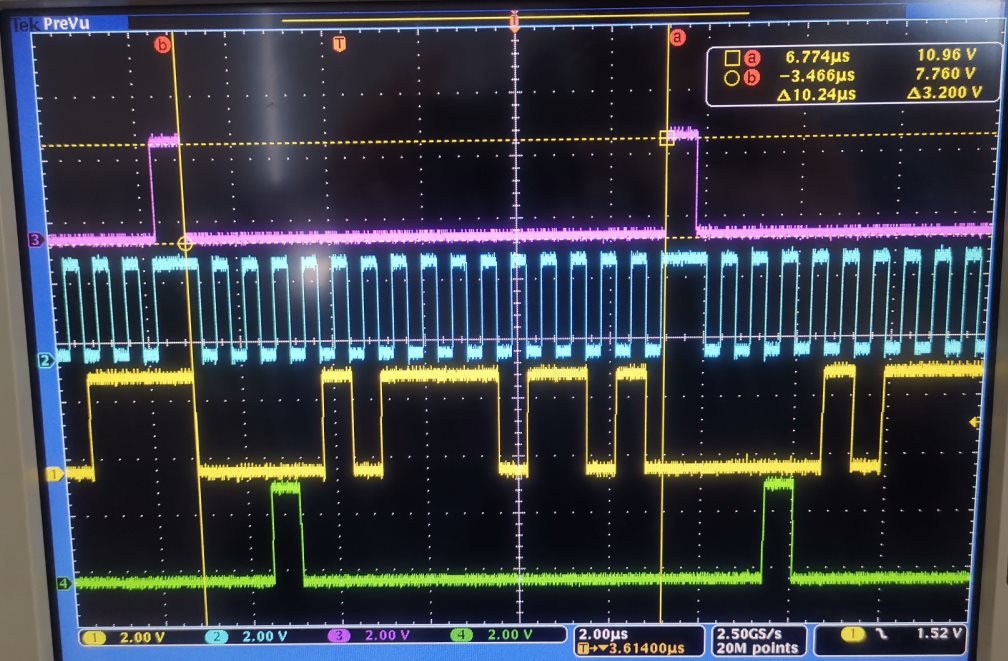

The waveforms of CS and DIN are not shown in the figure above, normally aaaa is shown below:

from top to bottom: CS, SCLK, DOUT, DIN

Can you give an explanation or suggestion about this?

The current SCLK frequency is 1.5625Mhz. Is the strange related to this? (Even though it's related to the strange, also want to know why it happened)

Thanks,

Luddy