Hi Bob,

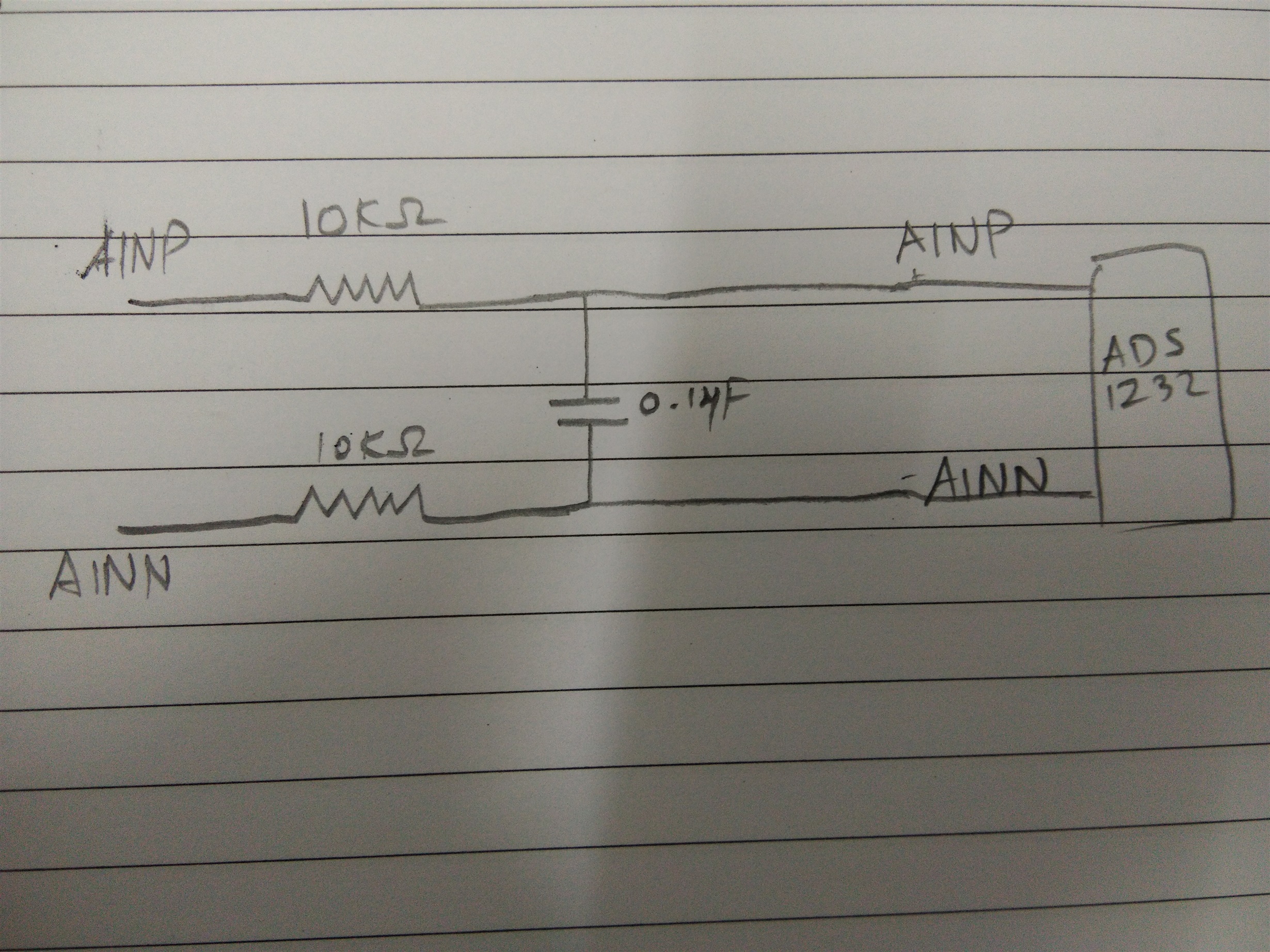

I am using a filter circuit for the input which I have attached. But I see wrong values in the input pins. Is there any problem with the filter circuit?. Also I have attached the screenshot of digital ground and analog ground that I have shorted. If it is a problem then should I connect the digital and analog grounds through an inductor?