Part Number: ADS1299EEGFE-PDK

Other Parts Discussed in Thread: ADS1299, ADS1298

I am Lead I ECG with the ADS1299. I have three electrodes connected to the board with the following configuration:

- LA - > CH1 +

- RA -> CH1 -

- RLD -> JP17 (Right Pin)

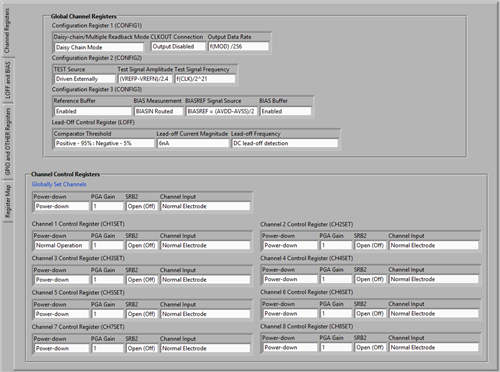

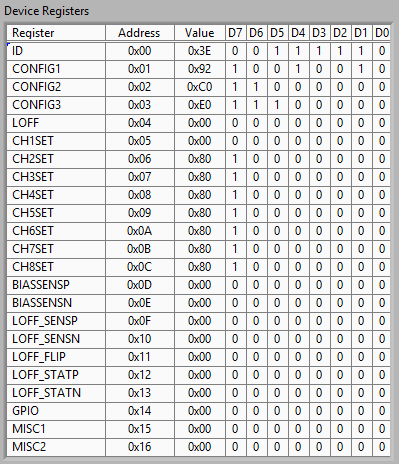

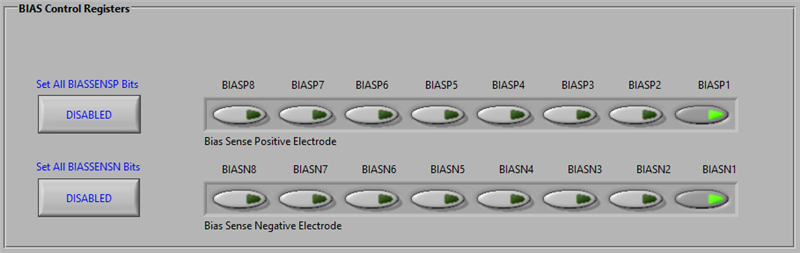

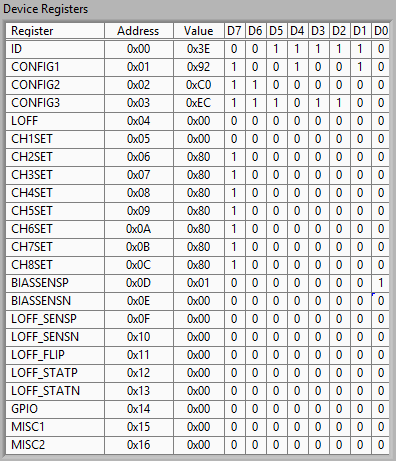

I have configured the ADC registers like this:

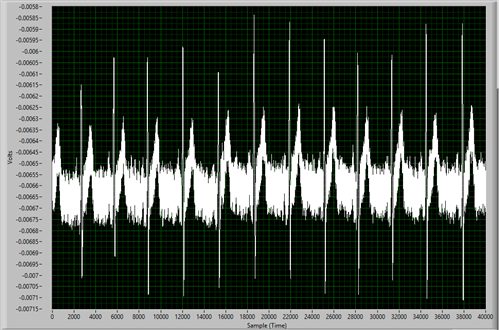

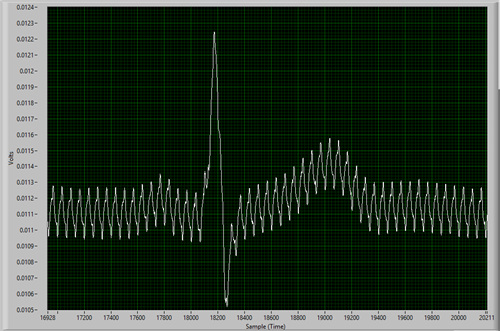

While the signal does look okay and clearly shows the QRS complex it is very noisy.

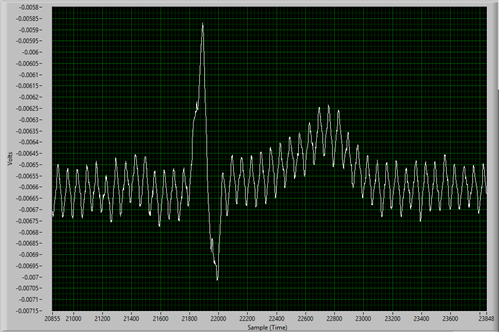

If I zoom in on one beat you can clearly see the HFN

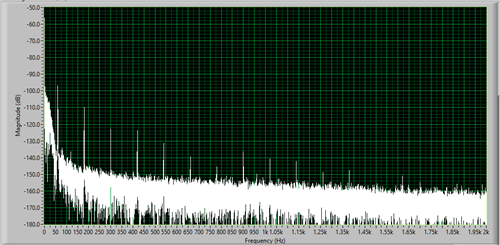

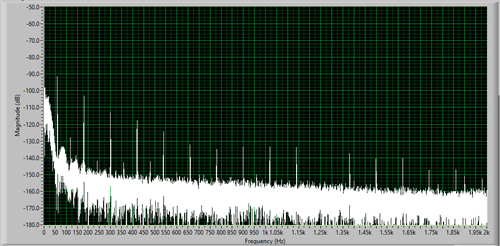

I believe that this HFN is powerline noise and the FFT of the signal seems to support that hypothesis.

I want to know if it is possible to remove it in the analog domain. I know that I can use some kind of LPF in post processing but I'm concerned about introducing a delay.