Other Parts Discussed in Thread: MSP430F5529, DAC81416, USB2ANY

Tool/software: Code Composer Studio

Hello,

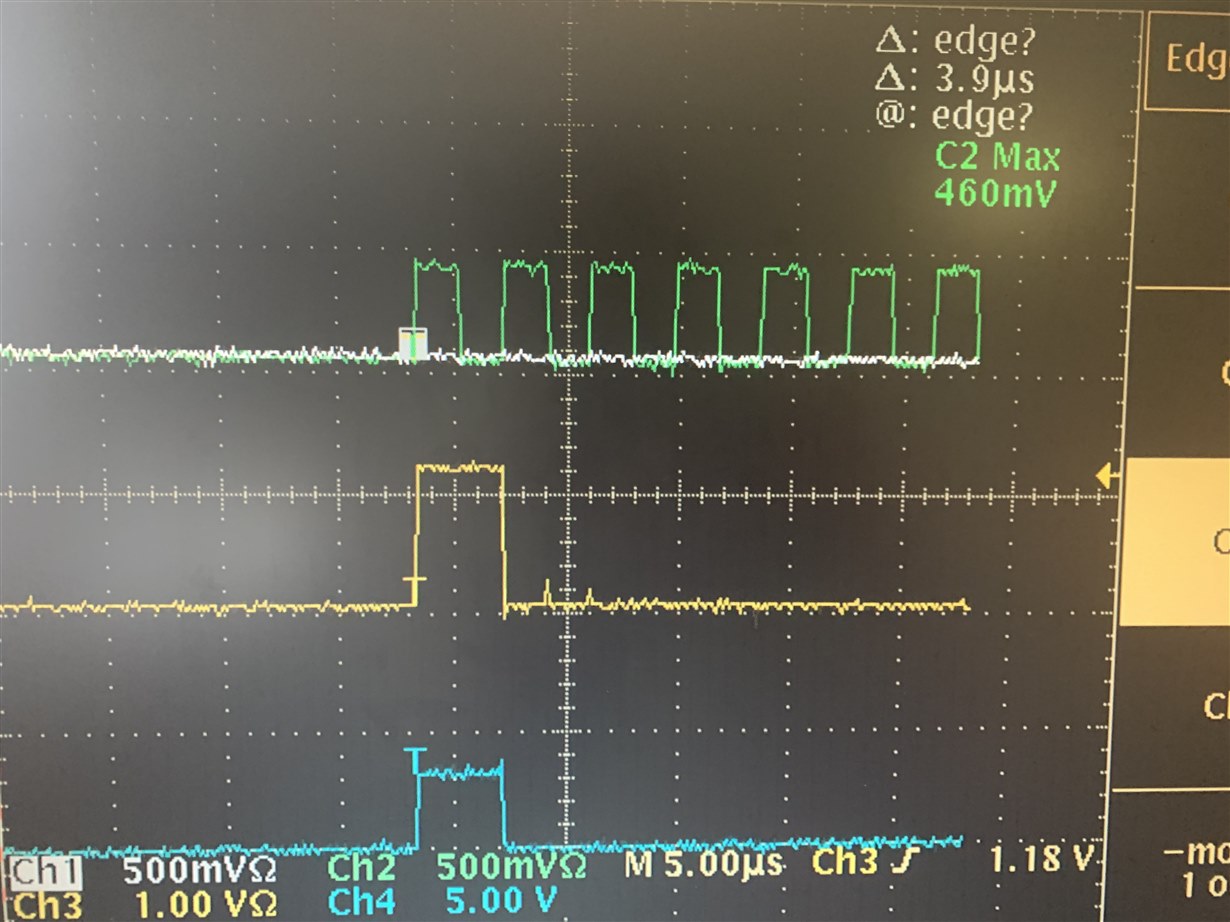

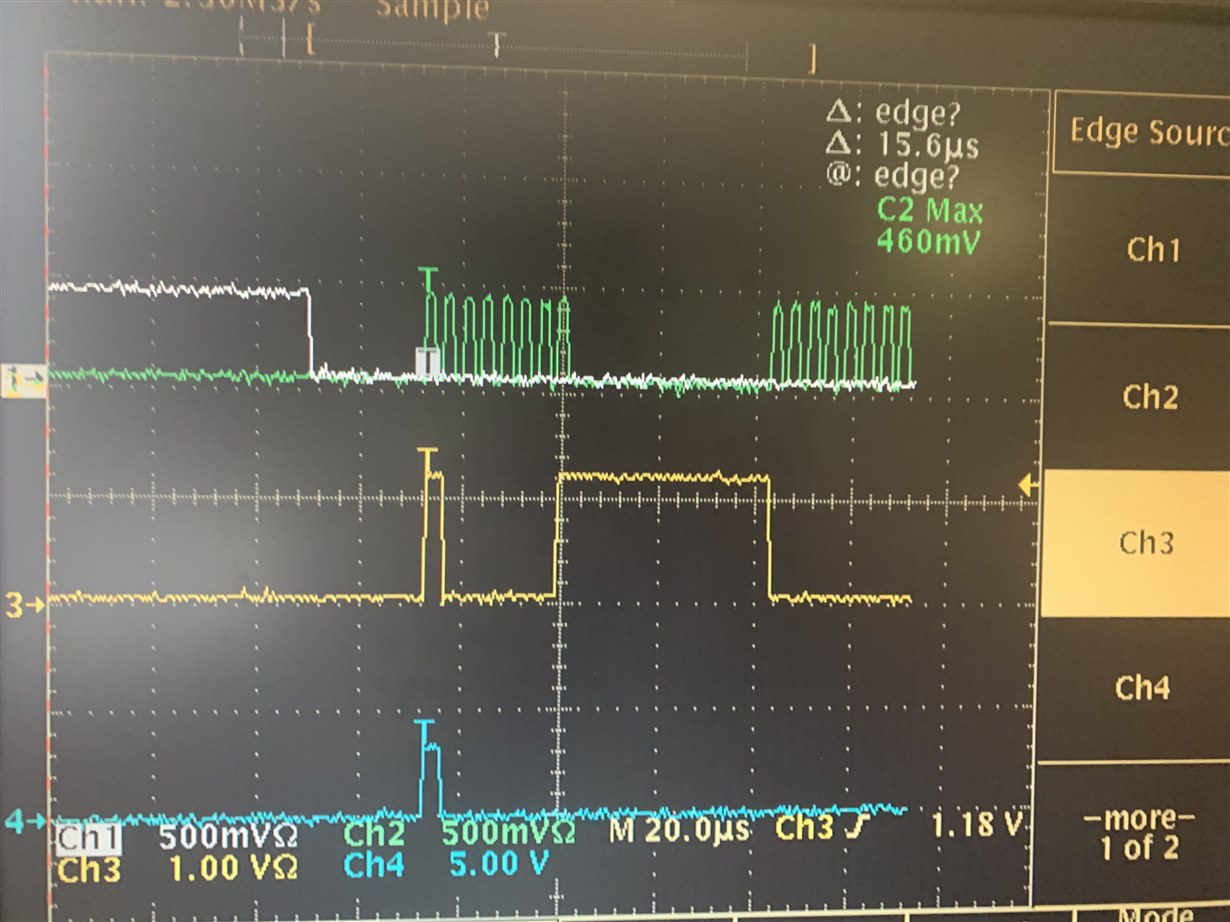

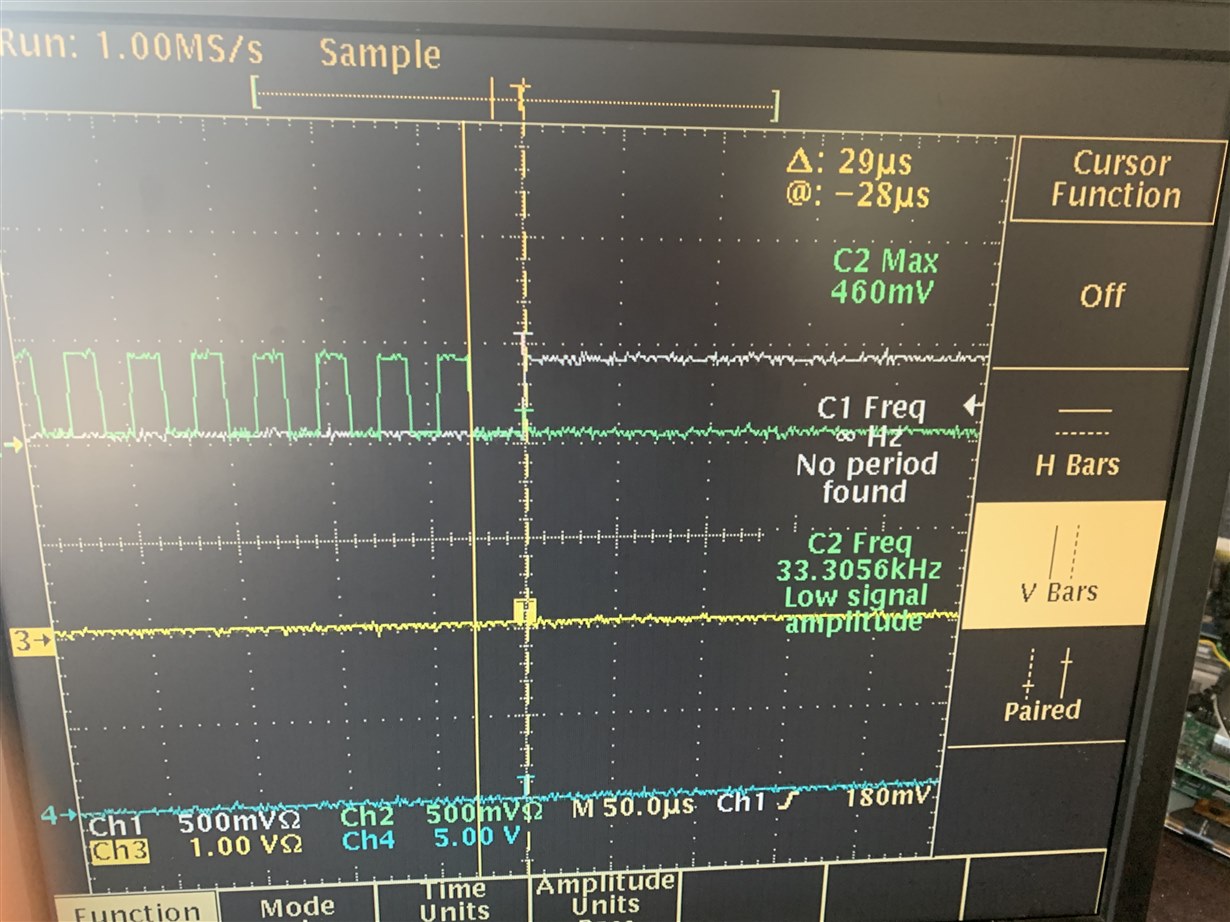

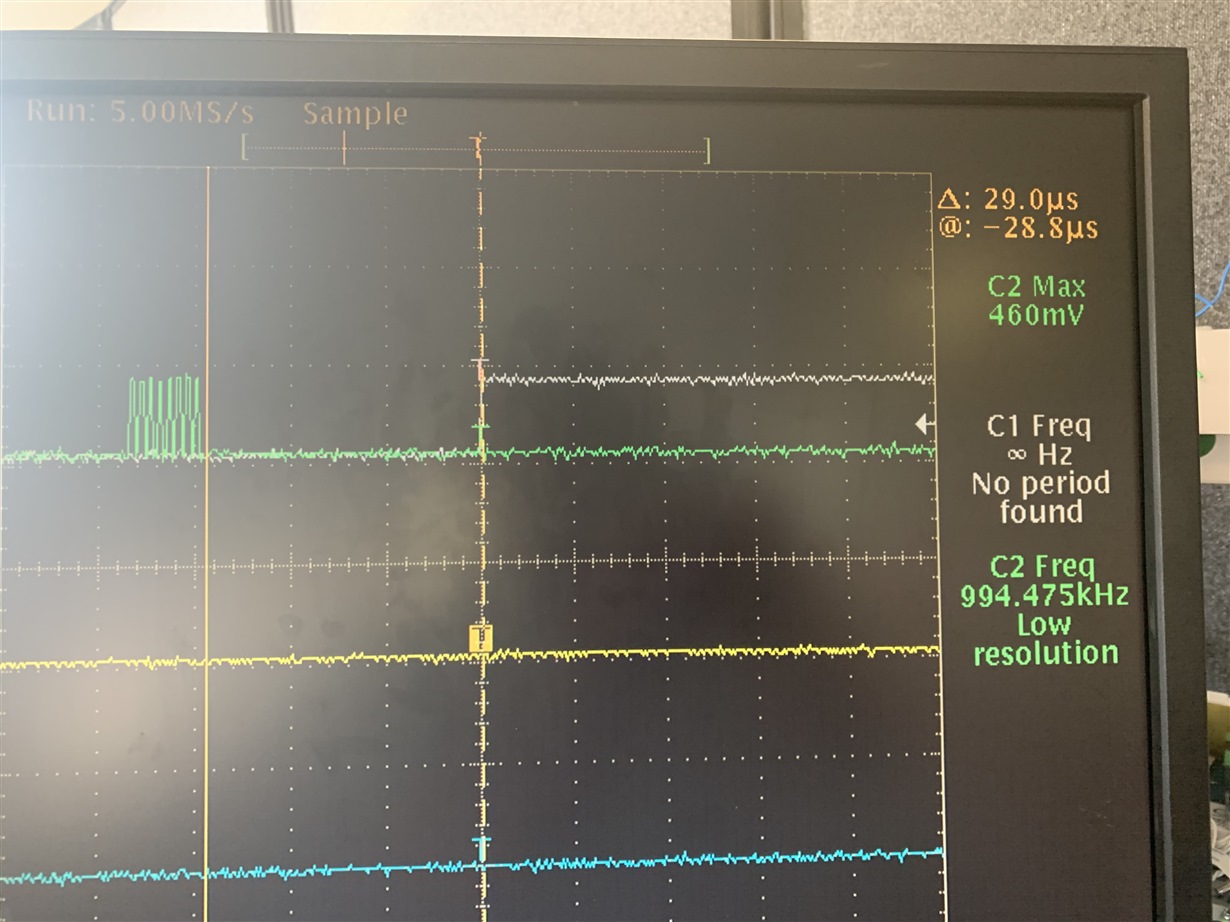

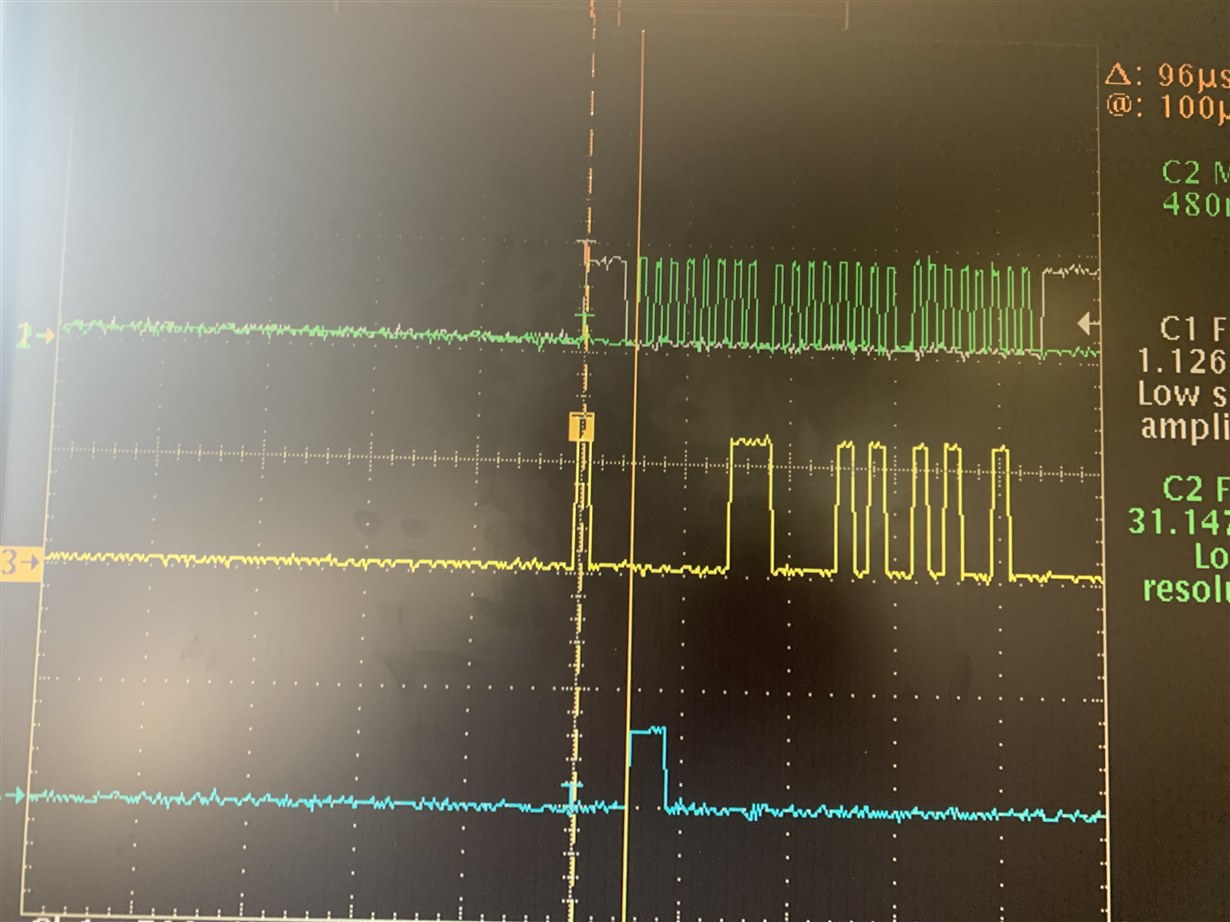

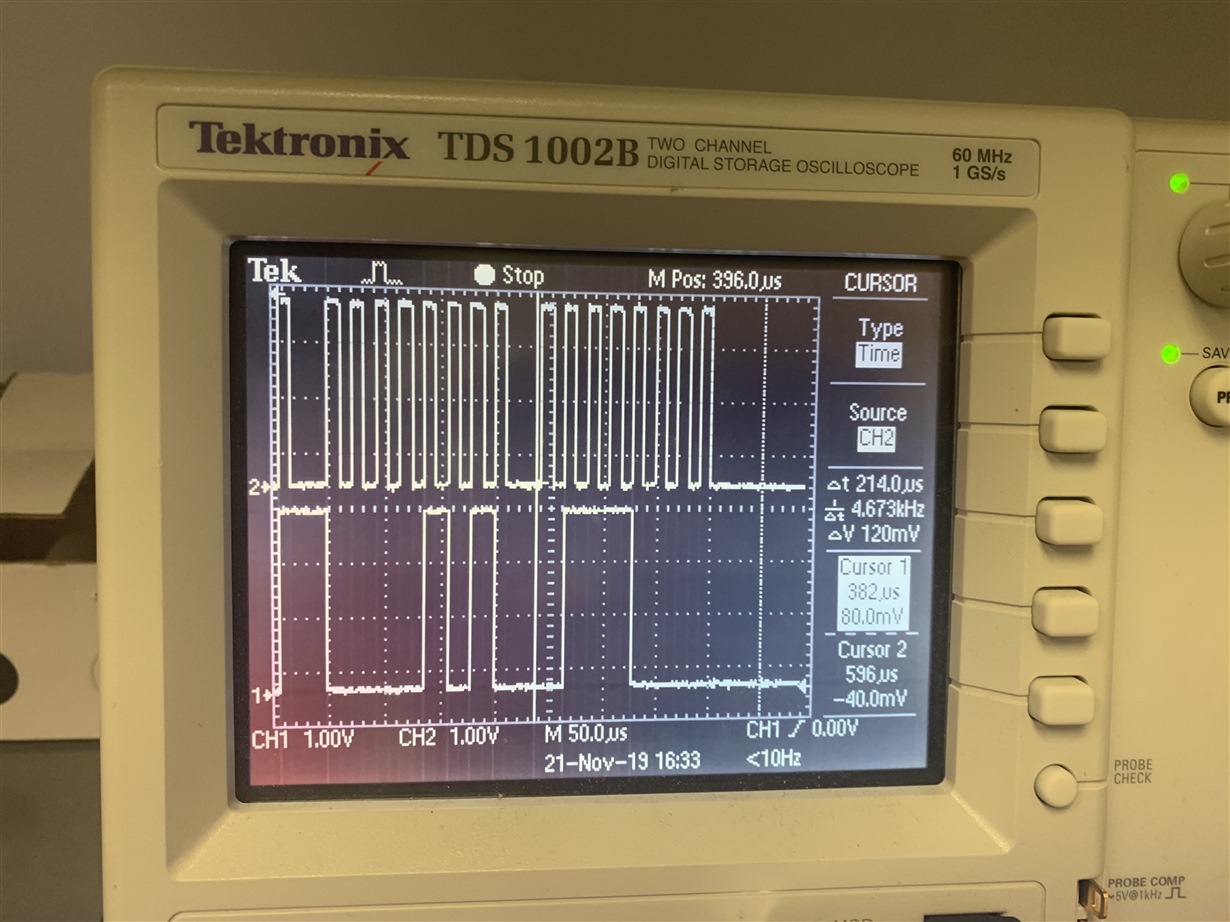

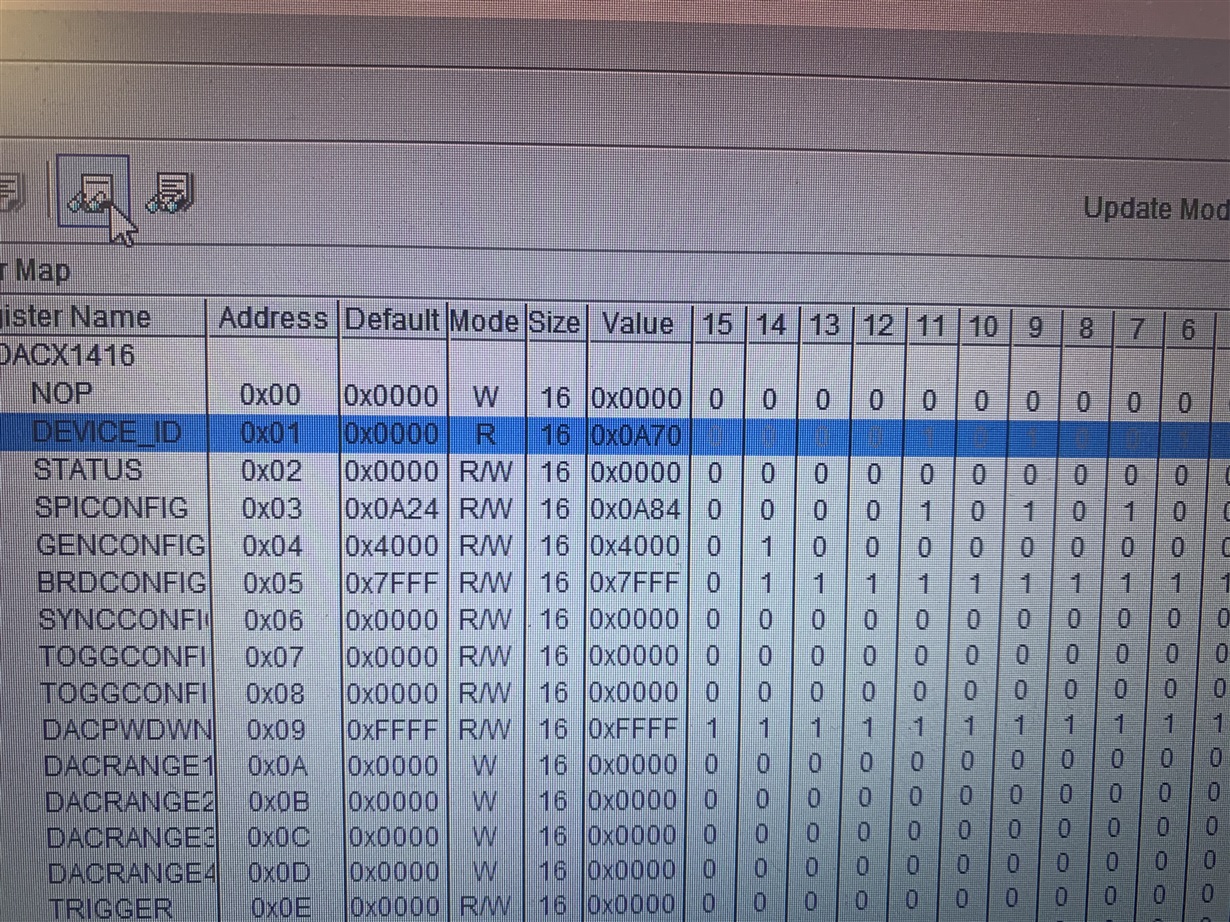

I am currently trying to connect the MSP430F5529 with the DAC81416 through SPI. I want to be able to read and write to the registers in the DAC, as a test I have made a simple program that reads the device id (0x29C0) and compares it to a constant. If the value read is correct, then the led (P1.0) on the MSP toggles indefinitely. I am having trouble getting SPI to work correctly. Here are the steps I am taking and some sample code I have prepared.

- set CS pin low

- spi_write: 0x81, 0xff, 0xff

- set CS pin high

- delay cycles. maybe needed, maybe not.

- set CS pin low

- write 3 dummy byes

- read the response into a buffer

- set CS pin high

- return (output[1]<<8) | (output[2]);// [0] = register echo, [1] = low part bits 16-8, [2] = bits 7-0

attached is my code, note SPI_POLLING is defined with -D as a global defined this is the non-interrupt state machine way of using the spi driver for lower level communication.

Thank you,

Andres