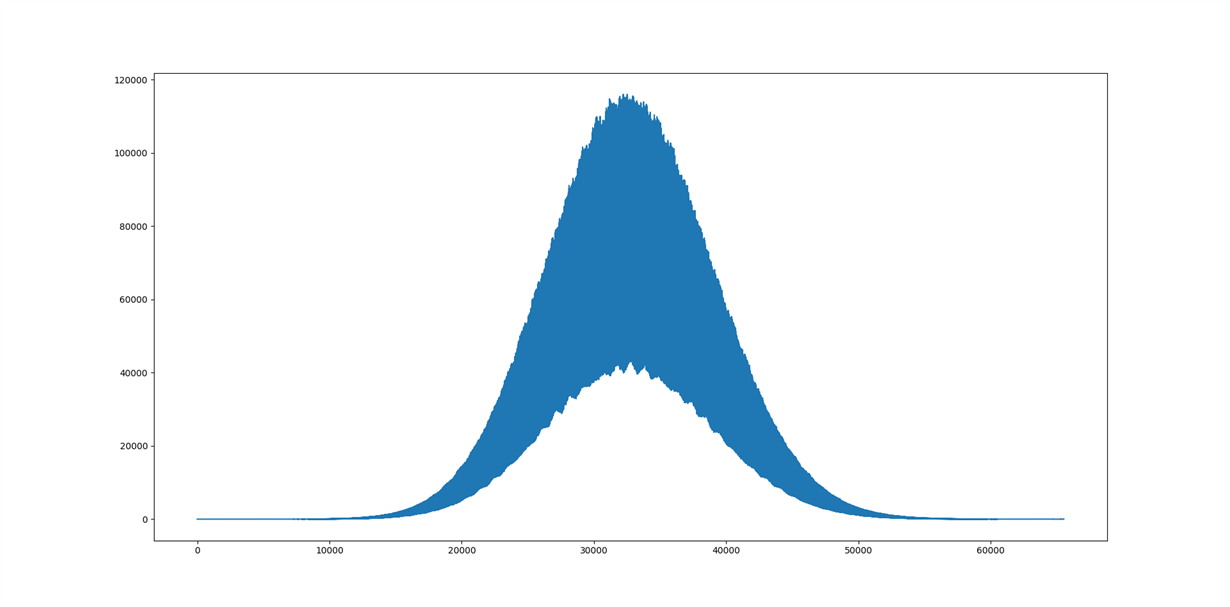

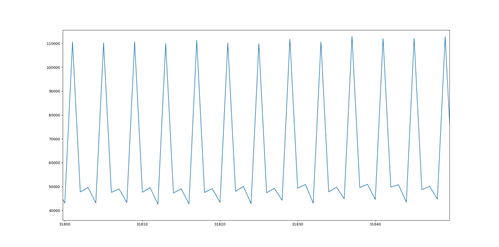

We have an ADS54J60 on an Abaco FMC120. We recorded Gaussian broadband noise (400 MHz bandwidth) with the 16 bit ADC from the ADS54J60 with a sampling rate of 1 GS/s. We then calculated the histogram by counting the occurrences of each of the 2**16 quantization levels. The result is shown below. The expected outcome is a Gaussian distribution. The measured outcome is that every fourth bin is about 2 to 3 times more probable than the adjacent 3 bins. DC offset was frozen for this measurement.

Histogram:

Zoom into the middle region: