Dear TI,

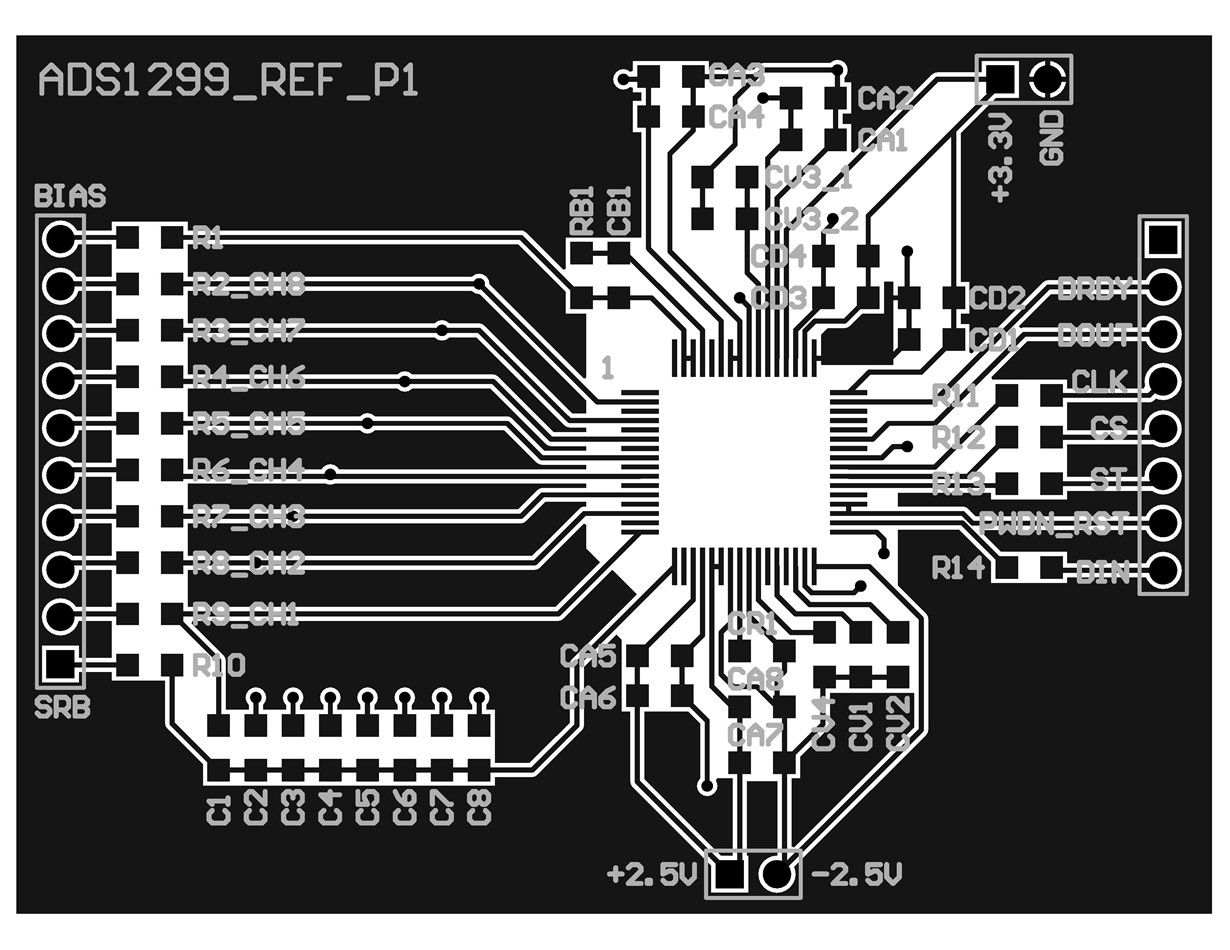

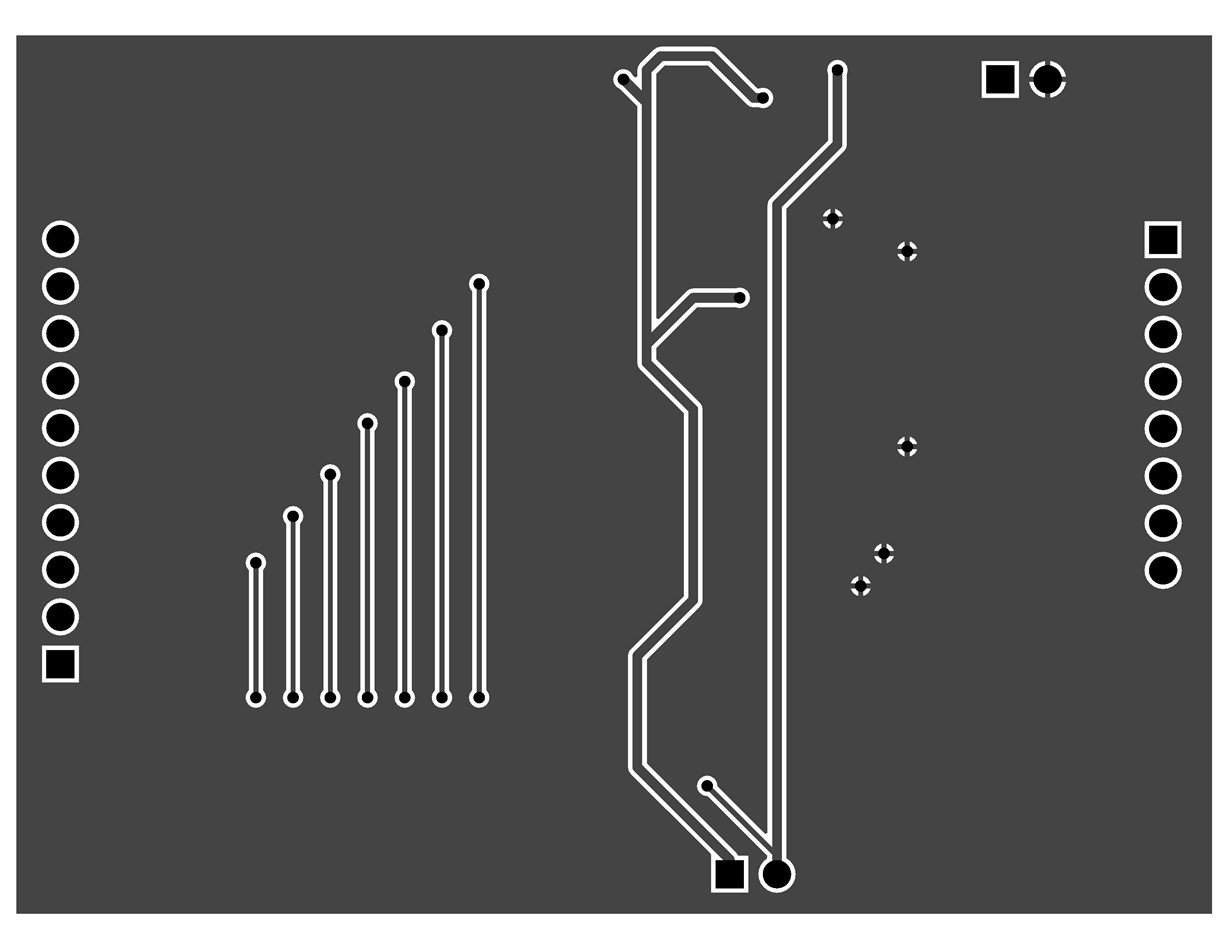

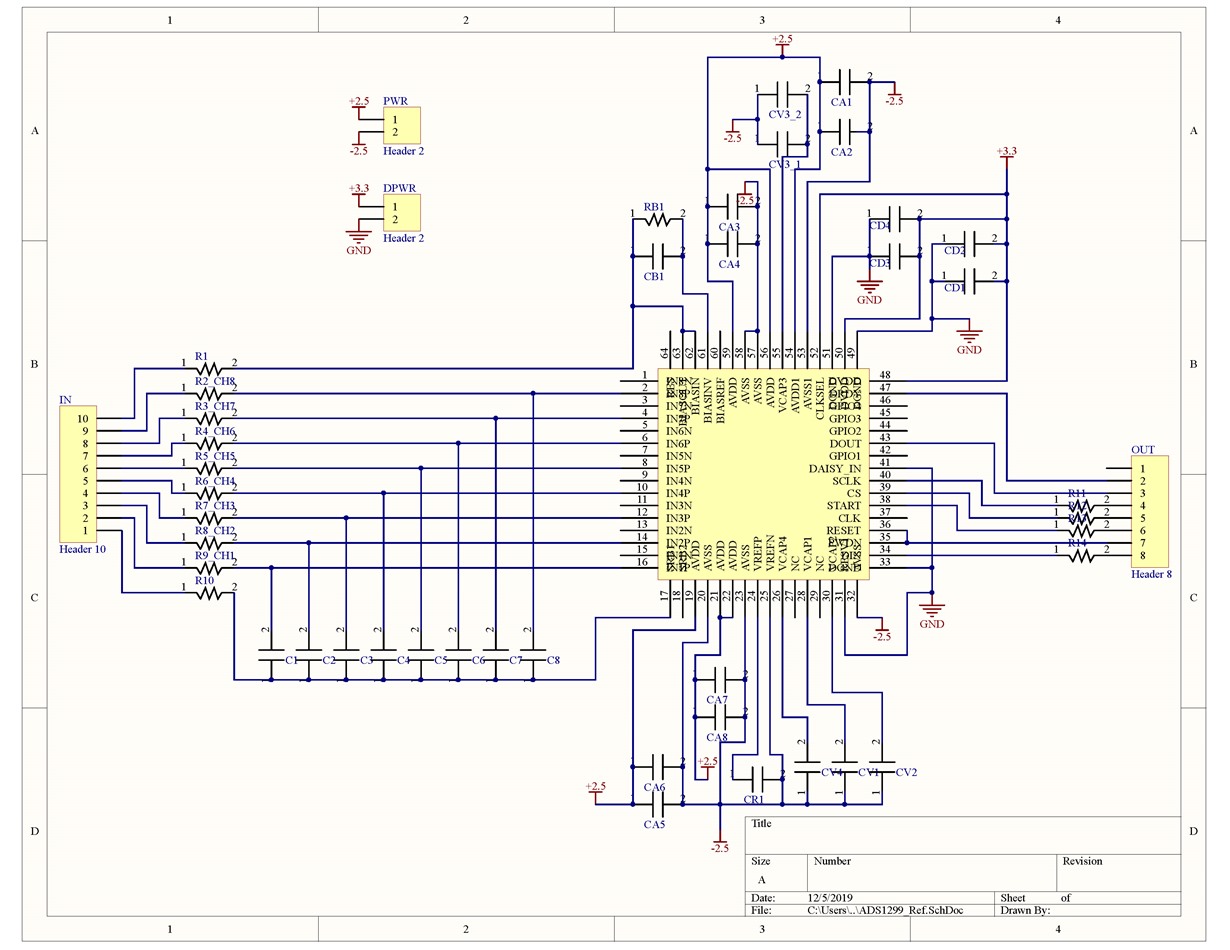

I'm trying to using the ADS1299 with the layout on datasheet p.73. (I changed the analog input to referential rather than differential.)

However, after I started the device and sent a reset command, the data rate is around 236.4Hz rather than 250Hz and has +- 0.1Hz change all the time (I put a probe on the DRDY pin), I also tested the internal clock signal which is around 1.94MHz. And the ID register is 0xDF which is wrong and is probably because of wrong power up sequence.

I think I did follow the power up sequence: tie every input to low before start-up and wait for 0.2 second then send a RESET. But I left the 4 GPIO pin floated, is that the cause of the problem?

Could any one give me some suggestions? Thanks in advance!!!