Hello,

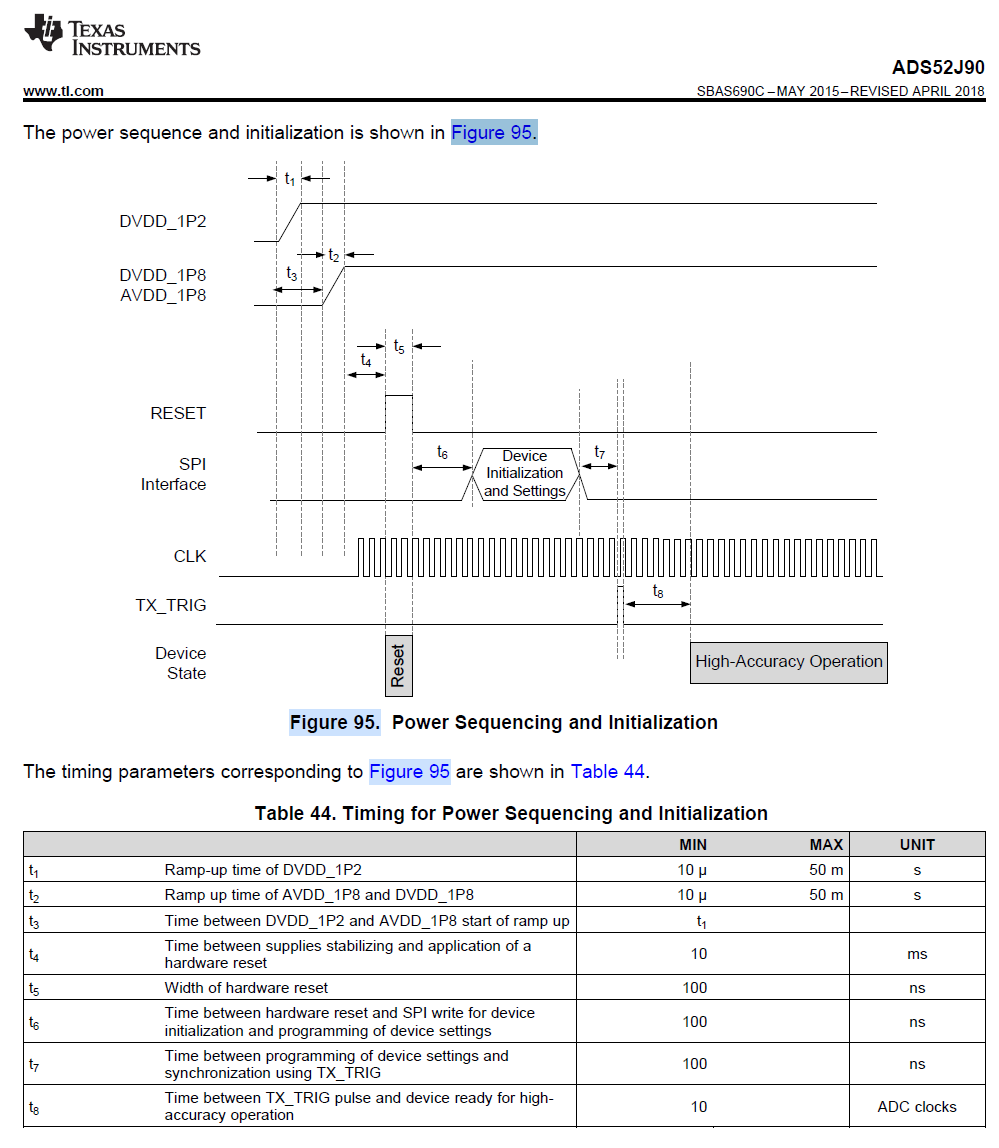

Our design uses two ADS52J90 ADCs. We wanted to revisit the startup timing specified in this datasheet section below, and ask for updated guidance.

First, we confirm that we are adhering to t1, t2, t3, and t4 from the oscscope capture below. t4 is easy to achieve because a human has to program the FPGA during this interval.

We read in another E2E forum post that TI recommends using a longer period for t5 than suggested in the datasheet. We also suspect that some combination of t6, t7, and t8 need to be extended. Our evidence consists of a long settling time on DCLKP and DCLKM (see image below). The data sheet says we could start calibrating the LVDS lanes in ~300ns plus the time to program the SPI. The screenshot below shows the DCLK still settling maybe 25us to 30us after reset at nominal conditions. This implies a longer t6+t7+t8 time than suggested in the datasheet.

Beyond this point, our design is still not stable. Do you have any comments about this specific startup observation? Or, more broadly, do you have other initialization-relevant community learning that we should know about?

Thank you!

Tyler