Part Number: DAC8760

Hi Support team

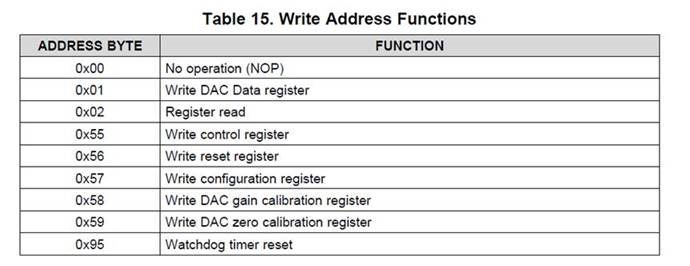

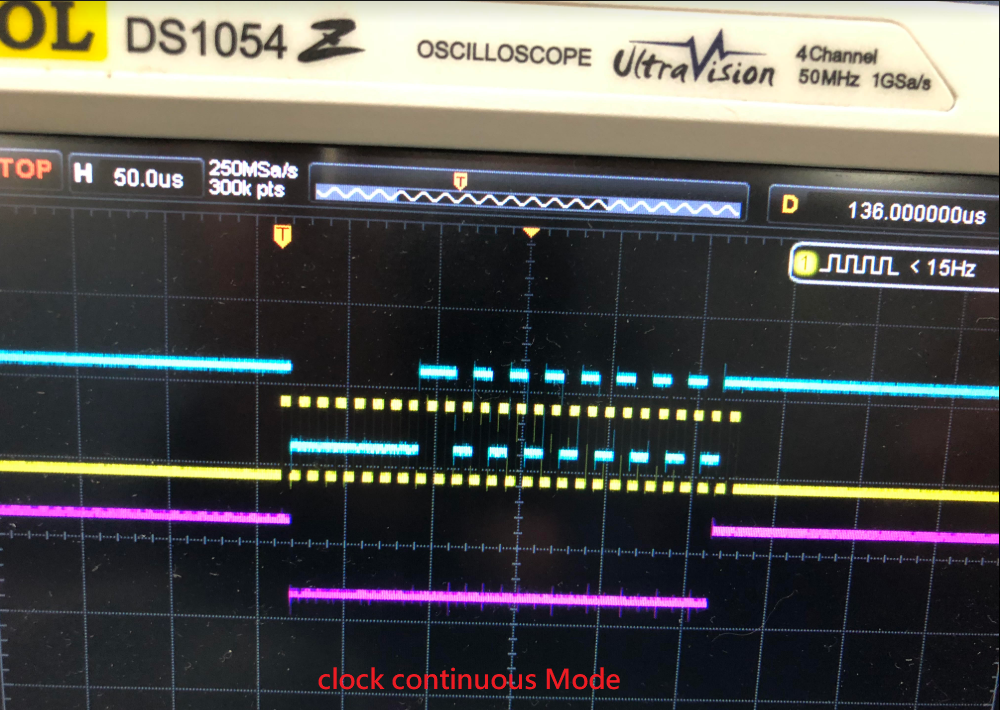

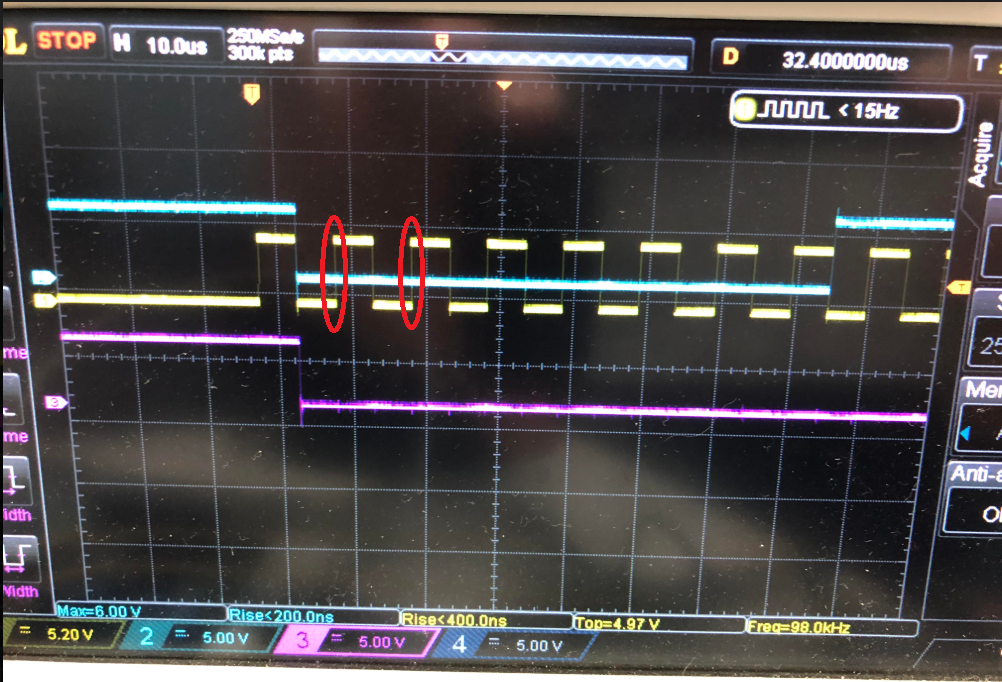

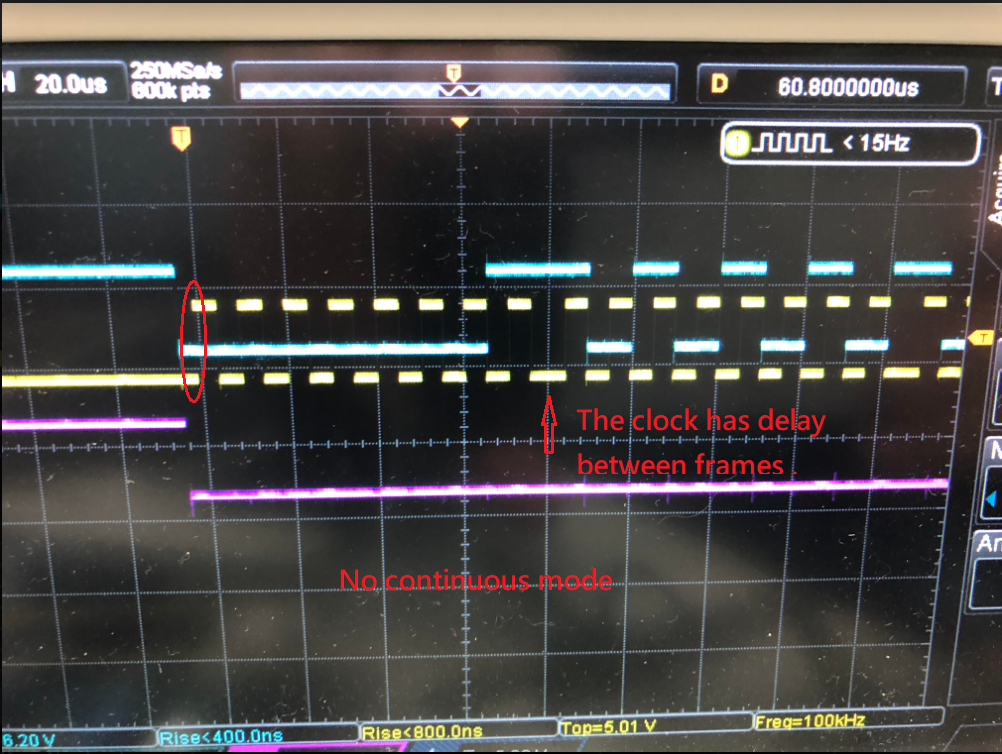

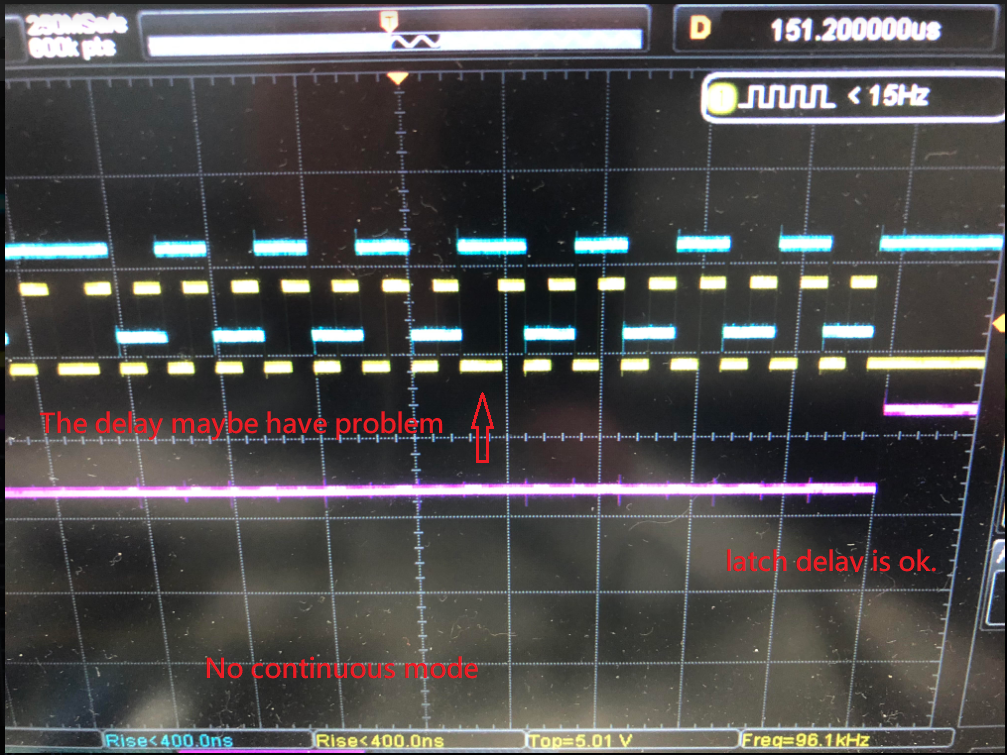

according to the specifications to Use 0x01 to write DAC data . Since it is 16bits resolution, I choose 0x7fff to output half level

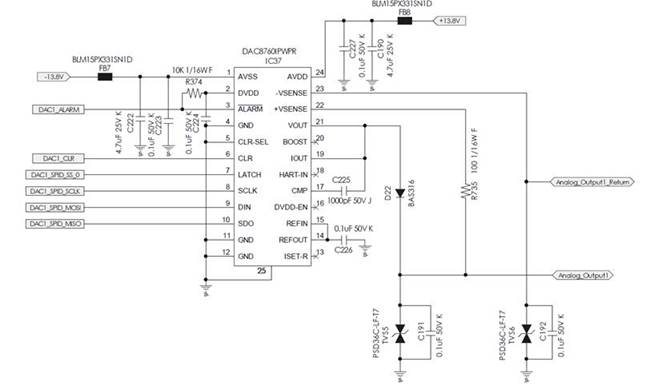

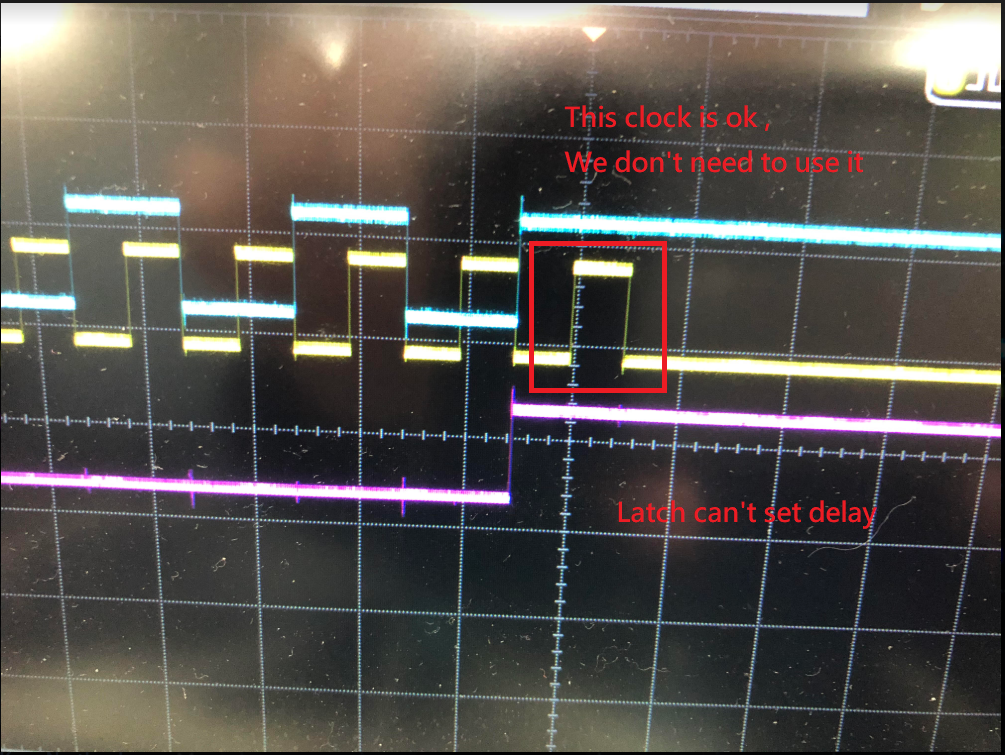

But check that the DAC does not have a corresponding output, check that the CLR is Low

if there is a place setting error or something else