Other Parts Discussed in Thread: LMH6401

Hi,

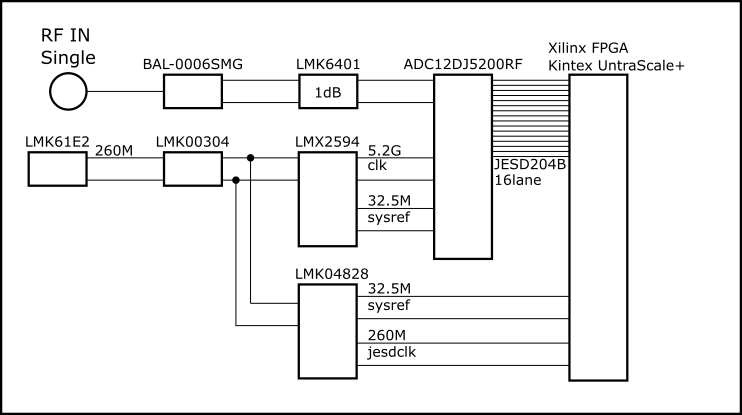

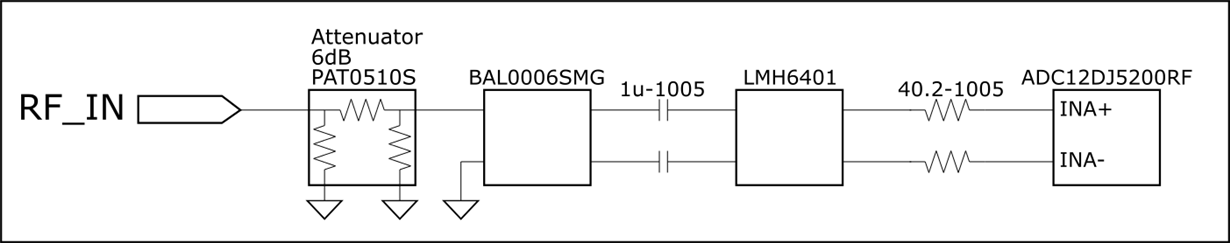

I am currently designing a board with an ADC12DJ5200 RF.

The circuits and ICs around the ADC were designed with reference to the EVM.

When the waveform input on the prototype board is plotted on a graph, the waveform may look as if it were modulated at 5.2 GHz.

Today's measurements were made in the following order.

cold start

66 MHz input

100 MHz input

133 MHz input

200 MHz input

1 GHz input

50 MHz input

66 MHz input

100 MHz input

133 MHz input

200 MHz input

1 GHz input

At first, only the 100 MHz input signal was not modulated at 5.2 GHz, and in the 2nd measurement, only the 100 MHz input signal was modulated at 5.2 GHz.

What could be the cause of the different results when all the environment except the input frequency is not modified?