Hi Team,

My customer would like to use the ADS4245, could you please advise regarding below question :

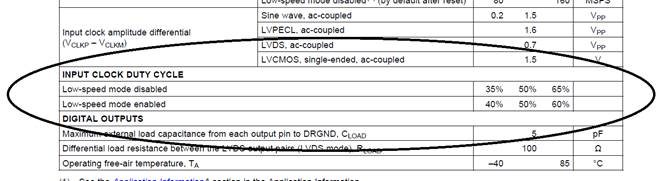

"I’d like to feed the device input clock by external clock of 36MHz with duty cycle of 33%.

I’ve noticed in the datasheet (see figure below) that the minimum duty cycle is 35% (or 40%). It means I’m out of spec…

How does it influence ADC performances ?"

Best regards,

Nir.