HI,

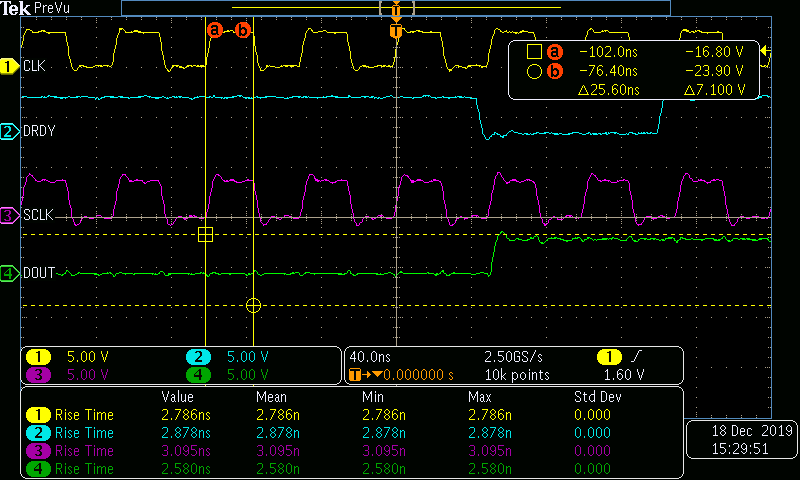

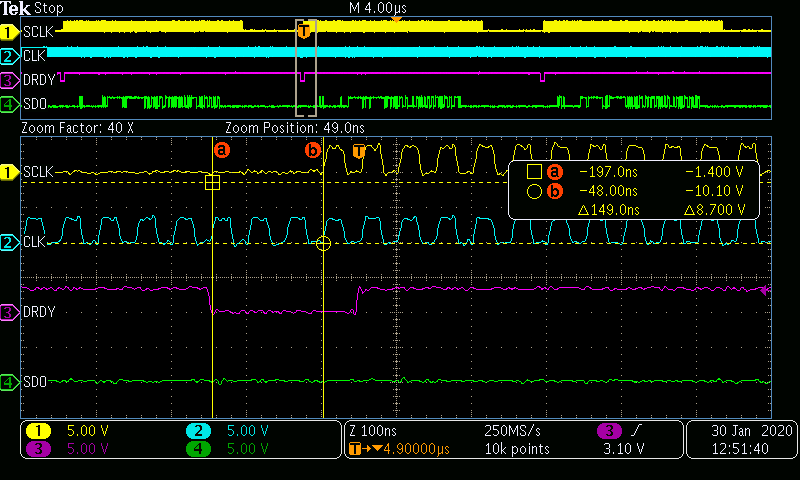

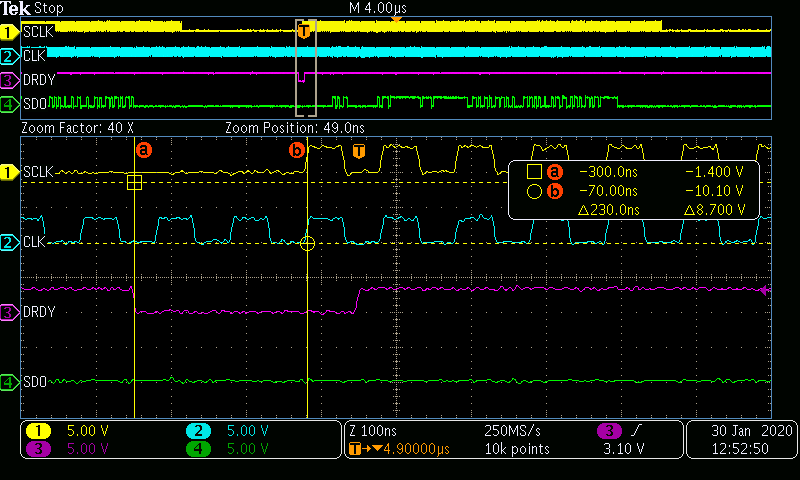

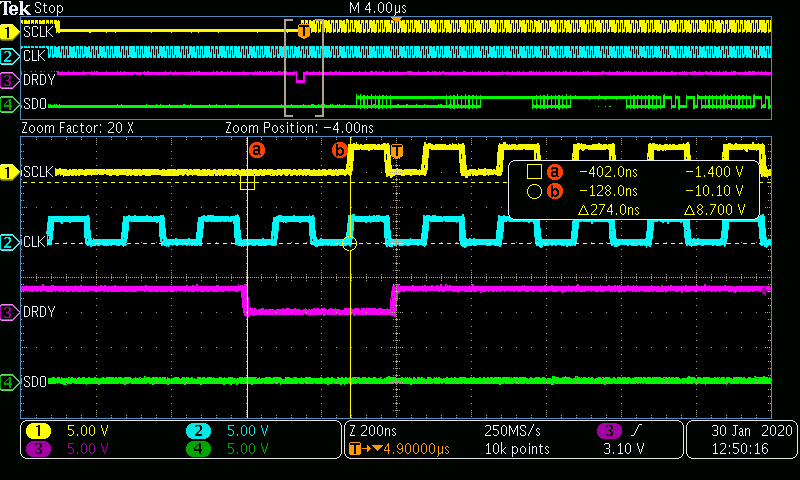

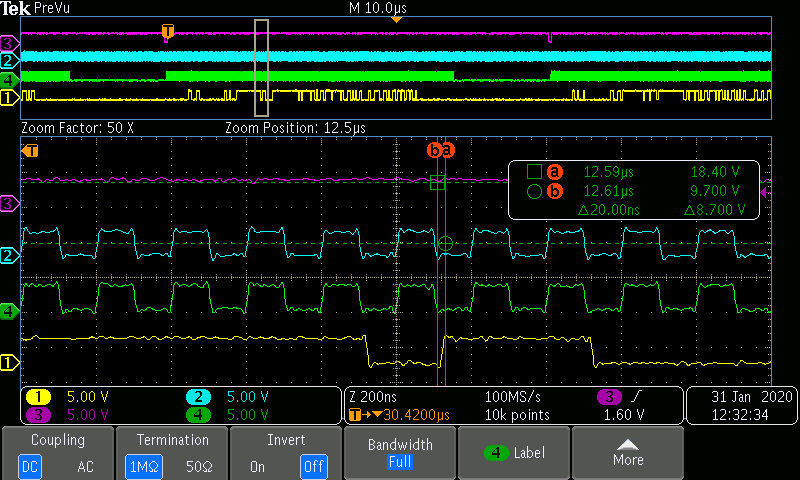

I have an issue in reading the data accurately when the SCLK / CLK is set to 20 MHz but reads accurately when clocked at 5 MHz.

Also when i probe at SCLK or DOUT line the ADC data seems to be ok.

Probe Capacitance helps shape the Timing delay in the SPI Timing characteristics.

I had built 9 boards and found 5 boards work seamlessly at 20 MHz and all the board work at 5 MHz.

Need to understand what would be the optimal solution to have in the design to have consistent performance.

????? current design have only series termination and no provision for RC ,suggest what can be done to improve-wise the design ??????

Reducing the ripple in the SCLK also solves the issue by having the LOW pass RC in series.

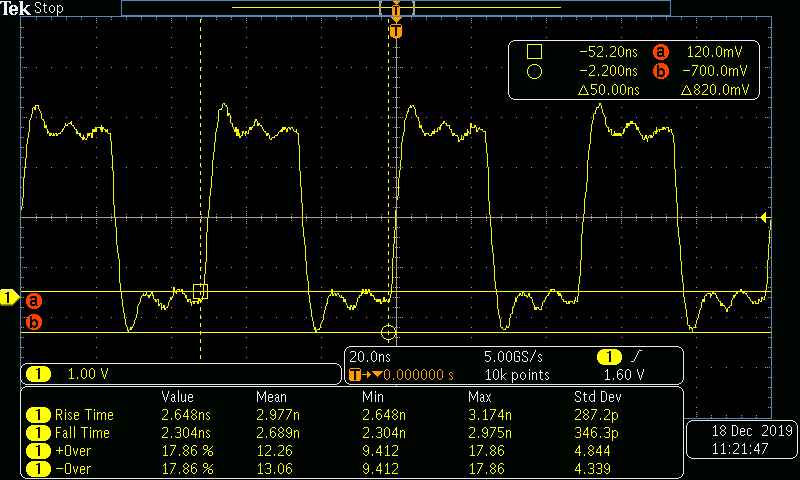

SCLK scopeshoot:

Current configuration is SPI and TDM mode in ADS1278 using 7 channels active.

Appreciate your help in solving this issue.

Thanks,

Mani