I am designing a board with the ADC12DJ5200RF.

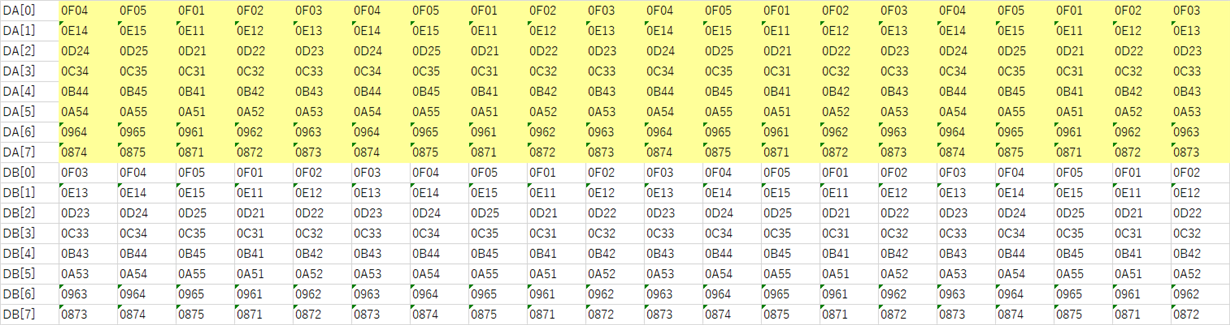

When I sent test data from the ADC to the FPGA using JMODE1, I noticed that the data sometimes deviated between 8 lanes of the DA and 8 lanes of the DB.

(If the FPGA receives the data correctly, I think DA [x] = DB [x], but it doesn't.)

Will it be solved by setting something on the FPGA side or by setting something on the ADC side?