Hi to all,

we use the ADC12DJ2700 on one of our own boards.

In some cases we have a special error with the ADC:

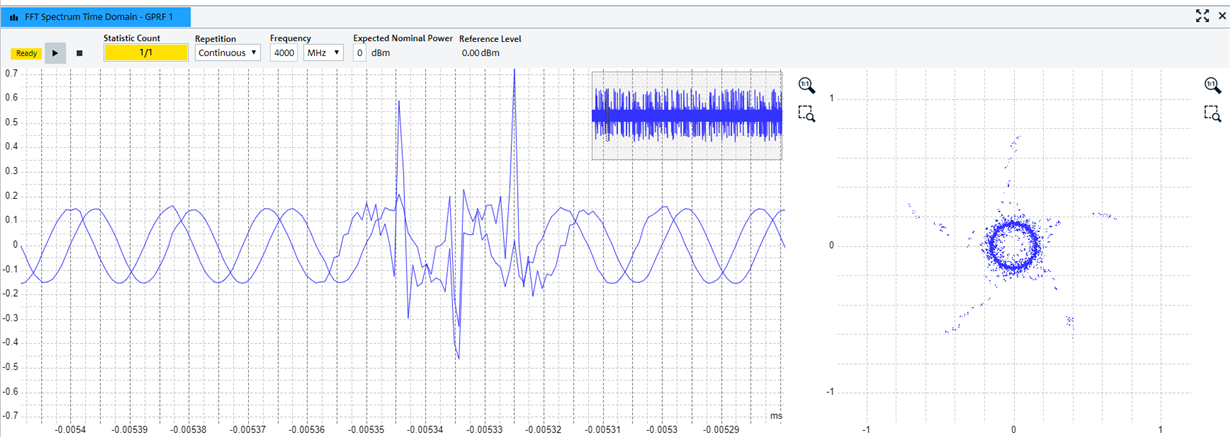

The noise floor in the spectrum is very high and seems to have a periodical ripple signal on it.

In the time domain we get a very ugly disturbed signal (testet with a sine signal an both ADC channels).

With the same setting and a new initialisation of the ADC we reach also an error free state:

Months ago I saw this behavior On the ADC12DJ2700 evalboard, too. But I assumed that this comes frome the early chip version. And after reinitialisation the error was gone.

Do you have any experience with this bahavior?

Is there any problem with the JESD interface? Which steps do you suggest to improve the JESD connection?

Very interesting: sometimes in the error case the OVL-output pins from the ADC shows an overload.

We configure the ADC in JMODE9 MODE.

It would be very great if can give some hints.

Thanks a lot.

Best regards,

Paul Rott