Hi,

I have a problem using ads1232,

only SCLK , DOUT/DRDY connected through series FerriteBead(200_ohm@100MHZ) to Micro,( two 27pf caps from those pins to GND are added in ads1232 side as low pass filter for UHF and GHZ noises )

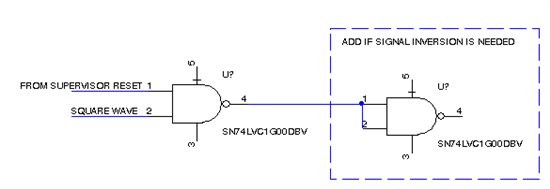

the /PDWN is connected to external reset circuitry that have voltage between 4.0 to 5.0 volts,( one 1k series resistor and 27pf cap exist here as LowPass filter )

it has a 500ms delay after powering up the digital and analog sections (pulls down the /PDWN pin) thus it is enough for initial reset of ads1232 !

the gain is set to 128 , speed for 10SPS , TEMP = 0 , A0 = 0 , AVDD = 5.0 , DVDD = 5.0 from different REGs , AGND , DGND are connected in one point near the main CAP of POWER ;

it works fine in the most of times, it has peak to peak noise in my system ( +- 30 ) nearly twice the ti_pdf mentioned, and I have stable readong of 60/8,000,000 = 133,000 counts , this is enough for my system.

the problem is here:

some times after powerup or in normal operation , the reading of a2d if shifted by -8500 ( eg: from 139,500 it jumps down to 131,000 )

( or from 310,000 it jumps down to 301,500 )

but the gain is satble..

and this unwanted huge offset will remain until :

1. turn off then turn on the system , sometimes removes the offset

2. manually pulling down the /PDWN to gnd by a wire! ( every time this will remove the offset temporarily , but the problem may occure some minutes later!)

3. using the 26 clock for internal offset calibration,( every time this will remove the offset temporarily , but the problem may occure some minutes later!)

because of unpredictable occurance of this issue , the system is unreliable,

what is the source of this ( internal offset registers UNcalibrator ) ????

what changes should I do for solving the problem?

Best regards,

notes on FerriteBead and cap

( I think the 27pf cap connected to ads1232 pins are small enough to have no effects in loading and changing characteristics of ads1232 )

( the FerriteBead(150nH) and 27pf cap make 82MHz corner frequency for LowPass filter for reducing EMI noises from Digital cpu side to analog side )