Hi Team,

We have the board up and running with DDC232CK. However, under test condition (test bit on , all input channels are disconnected) we are getting 0x1E00 instead of 0x1000 offset.

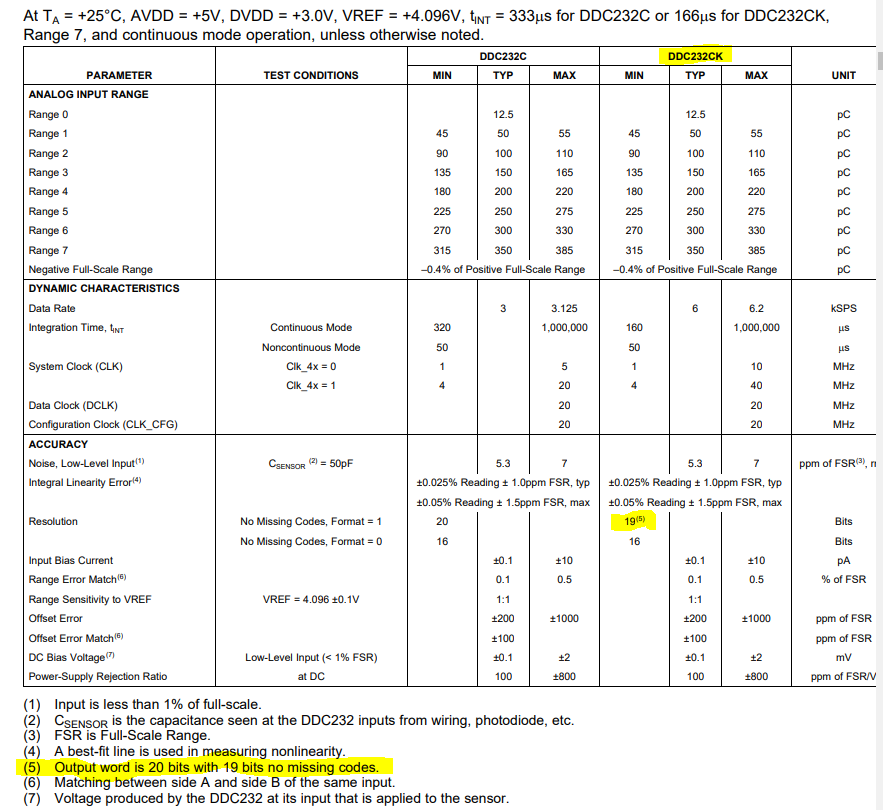

We think it might has to do with the output format. Datasheet indicates for format=1, there should be 19 bits instead of 20 bits for DDC232CK. The above readings were assumed output bits to be full 20bits.

If the output word is supposed to be 19 bits, the question is should we read out bits [19:1] ? or bits [18:0] or any other ways within the 20bit output word?

Thanks!

David