Hi,

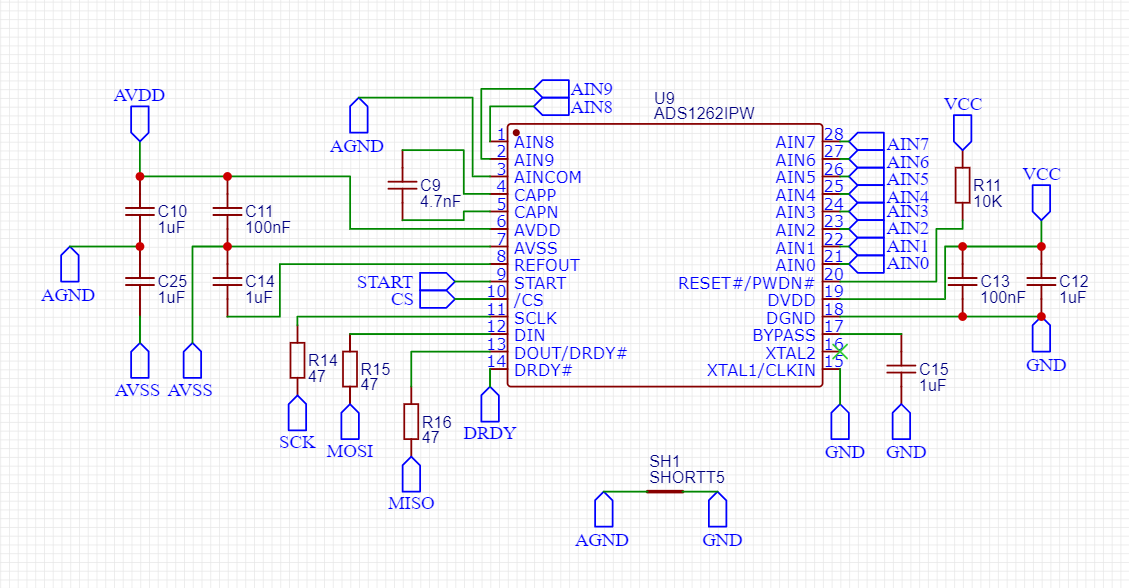

I have a problem with getting ADS1262 to work. The schematic of the ADC part of my device looks as follows:

The chip is powered up, START pin is held high by the MCR, bo I observe no pulse on #14 (DRDY). According to the datasheet, it should pulse @20Hz after startup with #20 (RESET/PWDN) and #9 (START) pulled up.

I observe the following voltages (all measures with the respect to DGND):

DVDD on C13: 4.54V with peak-to-peak ripple of ~170mV

BYPASS on C15: 1.91V (22mV ripple p-p)

AVSS on C14: -2.03V (180mV ripple)

AVDD on C11: +2.48V (80mV ripple)

REFOUT on C14: -1.97V (180mV ripple)

This chip also does not respond to SPI and the analog voltage supply lines are very noisy, but I think the lack of DRDY pulse is the core problem that should be solved beforehand.

Any ideas what's happening here?