Hi,

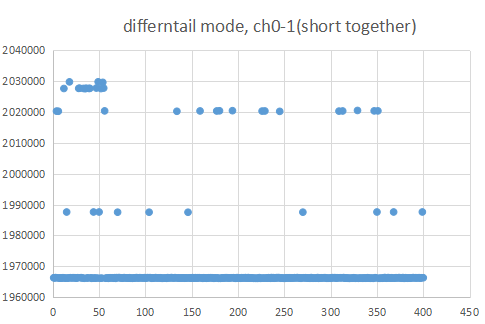

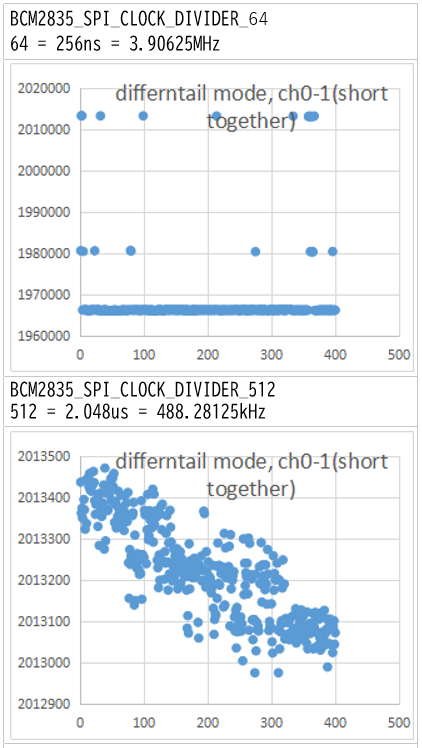

I'm trying to use the differential mode of the ADS1256(www.seeedstudio.com/Raspberry-Pi-High-Precision-AD-DA-Board.html) to measure input voltages in the range 0-5V, for 3 inputs(ch0-1,2-3,4-5).And I want to know device performance, so I connect together AINp and AINn by short pin.

I measured data for 400 points(Differential ,Gain 1, Buffer off, auto calibration off, calibration before measure by SELFCAL). This result data is attached. So, my questions is below.

1)Why result data is not stable? Why data is like steps?

2)This data accuracy is not good, So I want to compare my data(differential input measurement in short pins) to another. Does anyone have this data?

3)How to measure devices performance in my device? I try short pins and measured it. is this correct?

4)Which measurement method is best for this device?(ex. diff, buffer on, PG=1...)

Any idea? Thanks.

--

YH