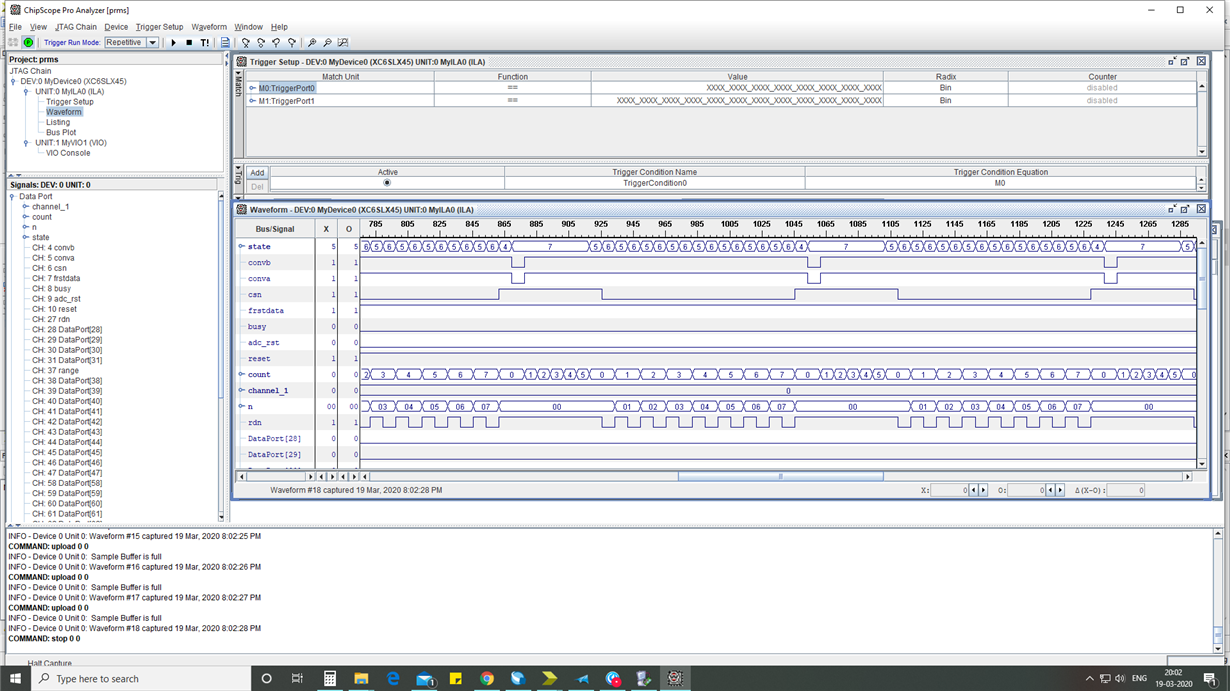

I am giving the conva and convb signal as per the timing requirement in the datasheet ,even though the busy signal is not going high.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.