Part Number: DAC80504EVM

Hello,

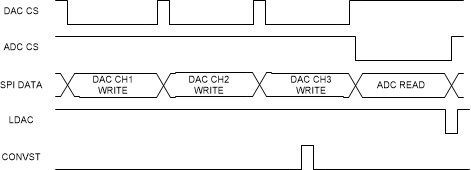

I would like to make a system which generates three different signals at the same time. Currently I am working with DAC80504EVM and as far as I have understood, with this DAC I can either have delayed transmission of three different signals or generate the same signal on all of the DAC outputs, since SPI can provide information about one voltage level at a time.

Since I want to control this generation with TMDSEVM6657 evaluation board, my current idea is to make a custom board with three one channel DACs, so that I can use all three SPI interfaces. I would use one SPI port and two McBsp ports from TMDSEVM6657 all clocked with the same clock. Does this make sense? I am not quite sure would it actually be possible to make all of it synchronized.

If there already is a TI evaluation board with these characteristics, or if you have some better ideas, I would appreciate if you could share if with me.

Kind regards,

Dejana