Other Parts Discussed in Thread: USB2ANY, , DAC8718, DAC7734

Hi,

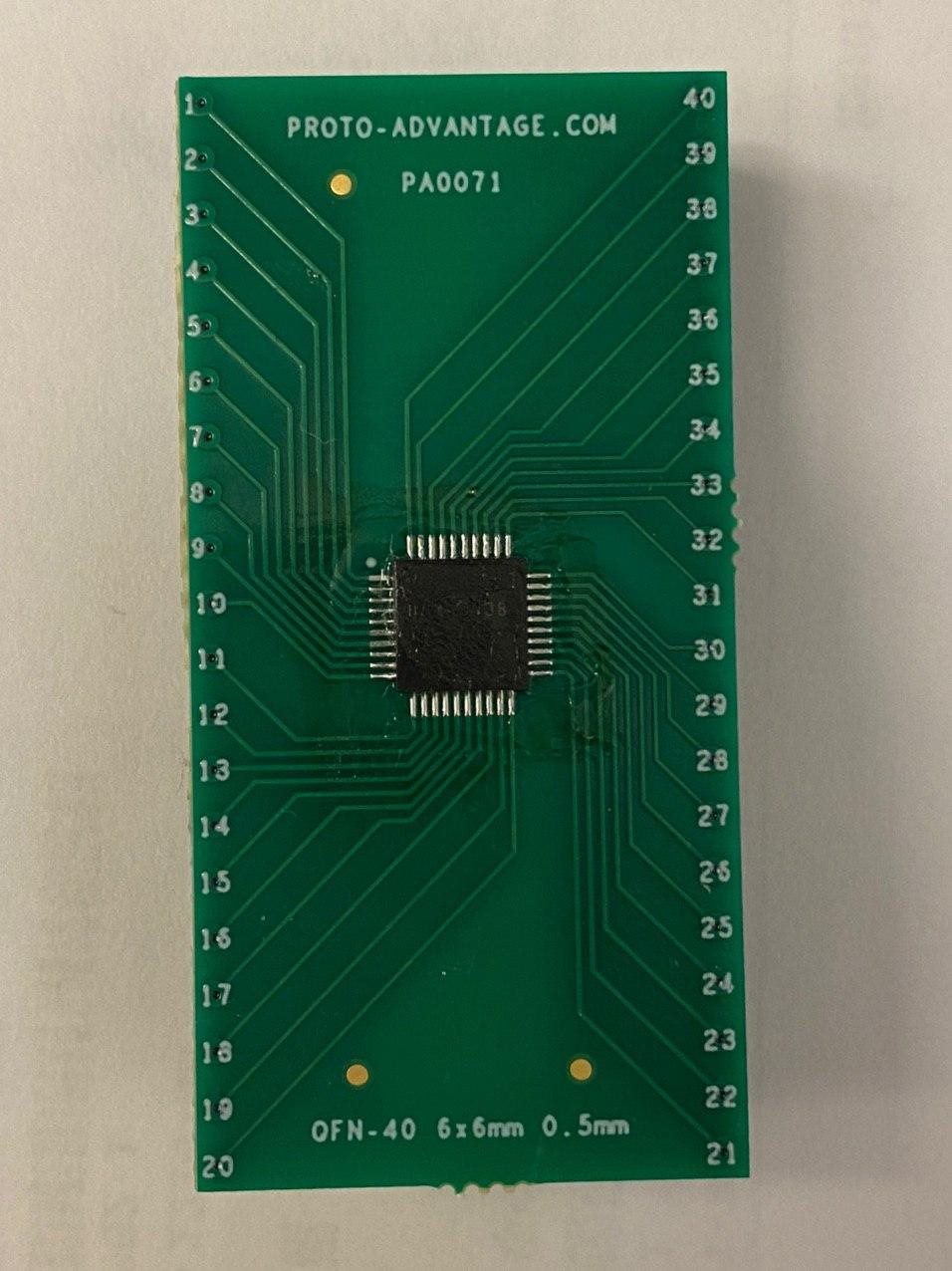

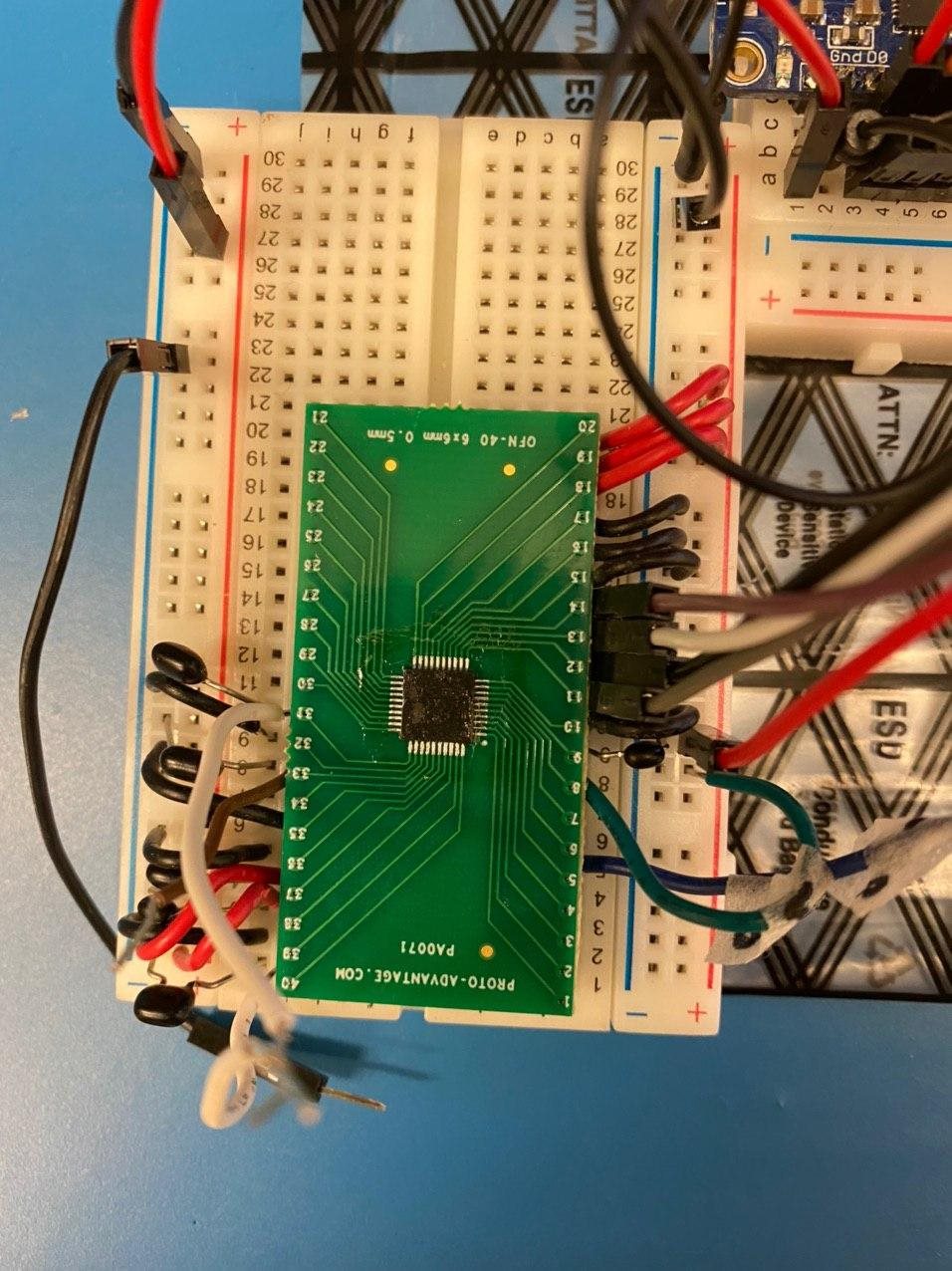

I have been trying to get this DAC work for a month. I even got the evaluation board twice, but not the USB2ANY interface cable. I tried interfacing to the DAC myself using python. I have used other DACs and they work fine.

So here's the issue with the DAC:

1. I see absolutely nothing in the outputs.

2. No SDO is issued.

So this is what I did for the DAC circuit (I'm not suing the evaluation board anymore):

Vcc = 10V

Vss = 0V

Vio = 5V (tried 3.3V and no response)

Vdd/Vaa = 5V

Vref = 5V

I Connect the CLR, RESET and LDAC pins to high (5V) so I don't have to worry about them until I can actually get a simple response from DAC.

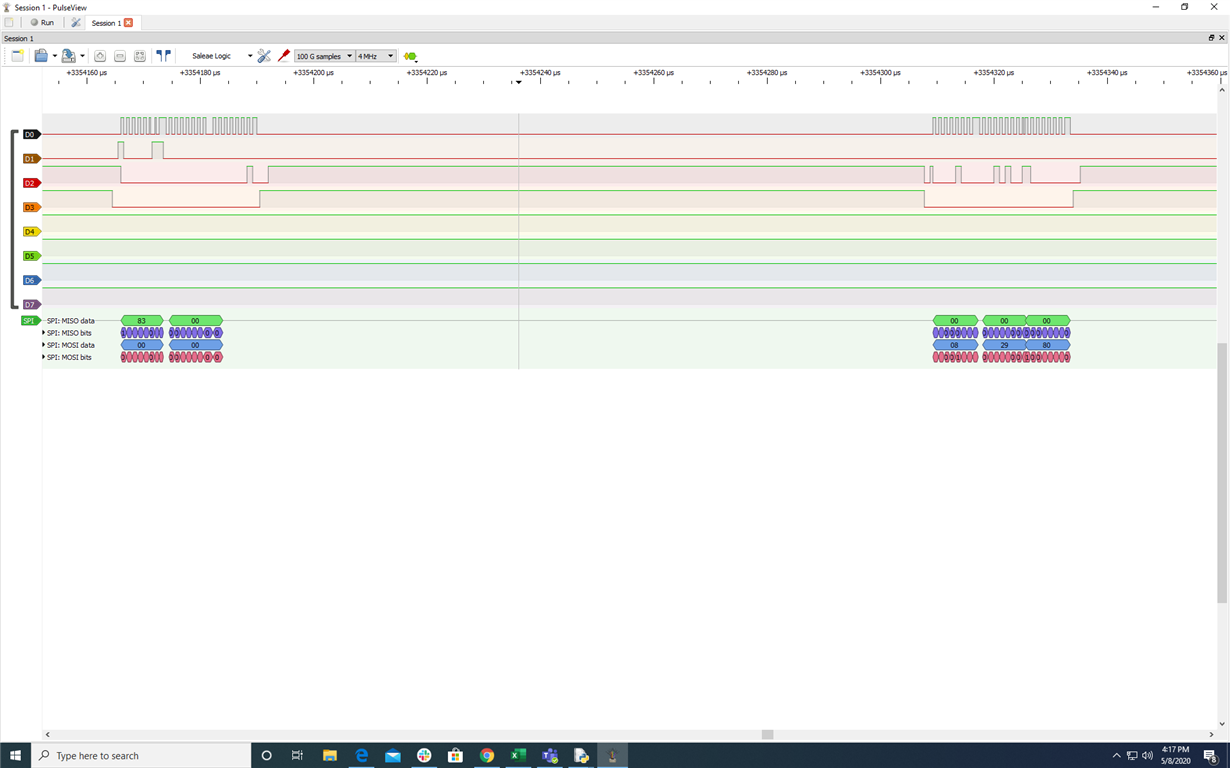

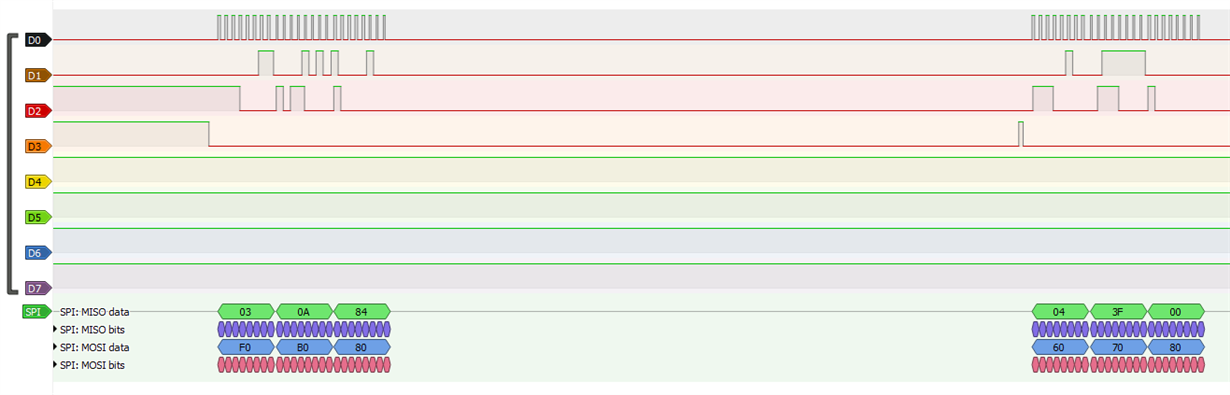

When I try to communicate with the SPI, here's what I do with the registers (obviously CS should go low before writing, no CRC, no LDAC, no broadcast, no toggle, no differential and in asynchronous mode... as simple as possible):

*First byte is to write to a register, and two other bytes are the data (based on DAC datasheet)

Trigger register = 00001110 , 00000000, 00001010 (I want to do soft reboot of the device before changing the registers)

SPI Configuration Register = 00000011, 00000000, 00000100 (I want to enable SDO and also, take the device to active mode)

DAC Power-Down Register = 00001001, 11110000, 00001111 (I activated all the DAC outputs, so no power-down)

General Configuration Register = 00000100, 01111111, 00000000 (I power-down the internal reference and use a 5V external reference)

And then I try writing to OUT0 ... but nothing.

Can someone please help me? I tried everything with the evaluation board as well to no avail.

Thank you!