Hello,

Under section 8.3.5 of the datasheet it talk about how to clock the ADC, I am getting mixed interpretations on how it is stated and I would like to ask some help for clarifications.

The first sentence of the paragraph says

"The master clock can either be sourced externally to the CLKIN pin or generated internally using the onboard oscillator that requires a crystal connected between the XTAL and XTAL2 pins

The second part of the sentence sounds contradicting to me, there is an onboard oscillator but would still need an external crystal oscillator? What would be the purpose of the internal oscillator if you need to have a external crystal oscillator anyway?

In the second to the last statement of that paragraph

"When not using the internal oscillator, turn it off to save power"

So there is an internal oscillator??

On the Clock Register the bit responsible for the the clock are these two

7 XTAL_DIS R/W 0b Crystal oscillator disable 0b = Enabled (default) 1b = Disabled

6 EXTREF_EN R/W 0b External reference enable 0b = Disabled (default) 1b = Enabled

So if i use a Microcontroller GPIO i have to disable(1b) XTAL_DIS, and enable(1b) EXTREF_EN. (Quite confusing for me because it could interpreted as to "enable (0b)" the the crystall oscillator "disable" thus disabling the crystal oscillator. Also what would happen if you forgot to disable the Crystal Oscillator , while you use an external reference, wwould it operate normally but just waste power?

Last that i would need clarification is

The development board seems to not synchronize the SPI SCLK as opposed to what the datasheet says.

DataSheet: "For optimal performance, the modulator sampling clock must be synchronous with the serial data clock SCLK. The modulator sampling clock is derived from the master clock which means the master clock should be synchronous with the SCLK."

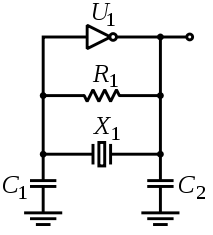

EVM DataSheet: "The ADS131M08 requires a continuous, free-running external master clock at the CLKIN pin for normal operation. The onboard complementary metal oxide semiconductor (CMOS) crystal oscillator (Y1) provides the nominal 8.192-MHz clock frequency used in the high-resolution (HR) mode of the device."

Does this mean that its not as critical to synchronize the SPI SCLK and CLKIN ??

Thank you.