Other Parts Discussed in Thread: TMS320F28388D, C2000WARE

Hi there,

I am planning to use the AMC1210 together with the TMS320F28388D, because I have in total 12 Sigma Delta Modulators in the application. As I need to get the data from the AMC1210 as fast a possible, I decided to use the parallel interface of the AMC1210. The EMIF1 interface of the TMS320F2838x is already connected to a 16-Bit SDRAM, that is selected via CS0.

Now my questions are:

1. Can I connect the AMC12010 to the EMIF interface?

2. Can I connect it in parallel to the SDRAM and select the AMC1210 via e.g. CS2?

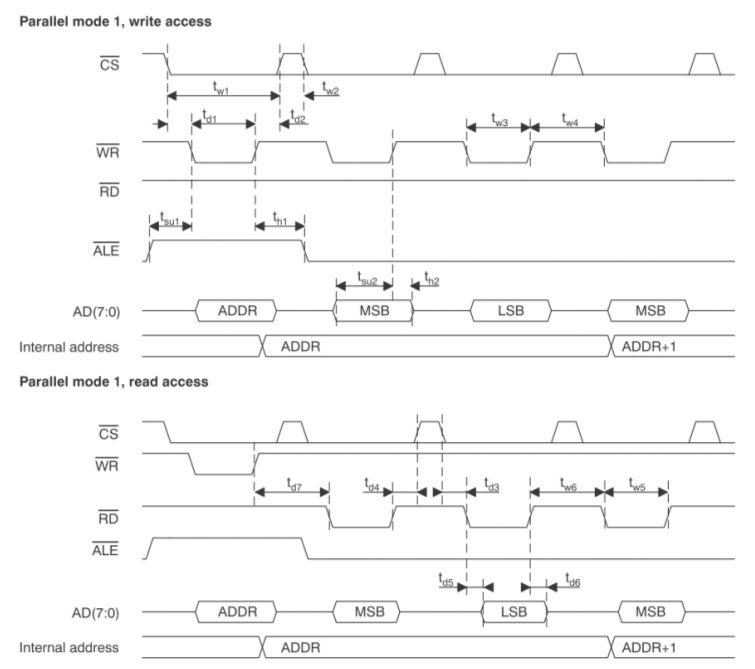

3. Is there any connection example for the parallel interface? At first glance I was not able to match the AMC1210 pins to the EMIF interface.