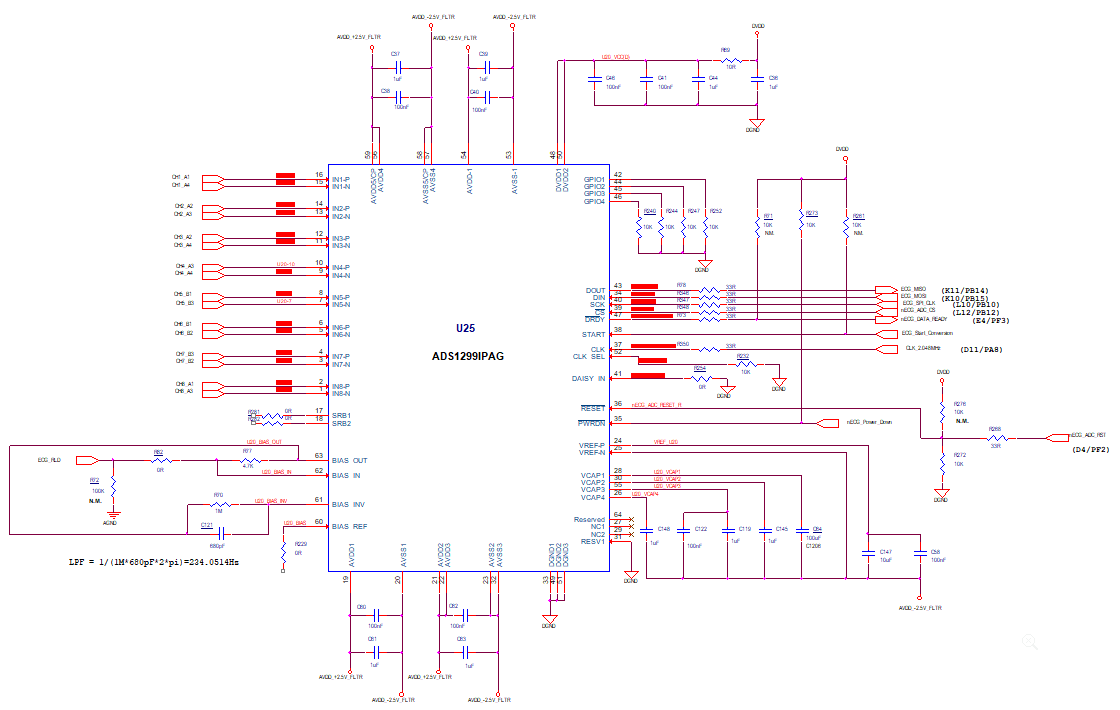

I need some technical assistance for the following issue. Using the part number ADS1299IPAG

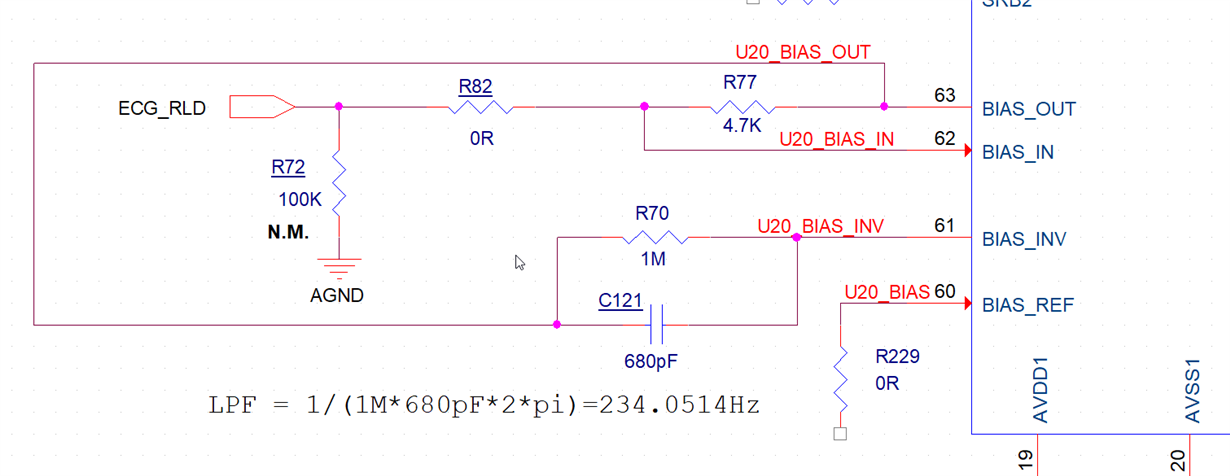

I am observing un-wanted and un-intended pulses on the bio-potential channels and suspect that the root cause of these pulses is the RLD pin.

This occurs when all of the bio-pot channels (incl RLD) are open, meaning not attached to the skin or any input resistance, but rather "open" or "in the air"

(And they do not occur once bio-pot electrodes are attached to skin).

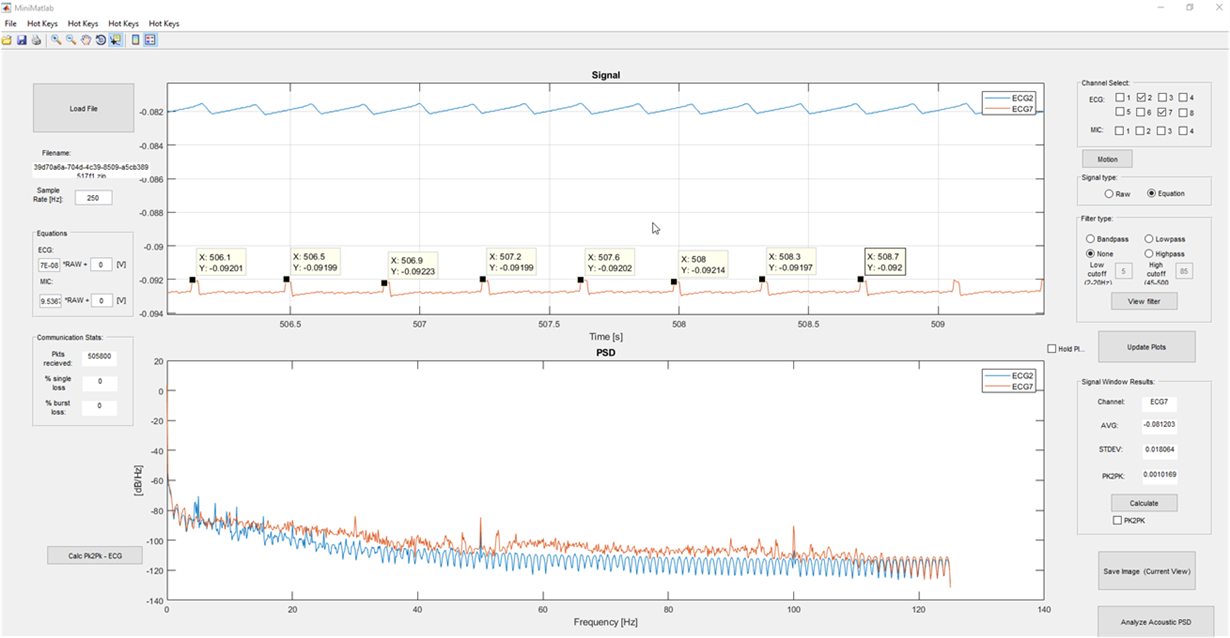

the pulses observed are:

amplitude = 1mVpp

frequency = 2.5Hz

duty cycle = 7.5% (meaning pulse width = 30msec, pulse duration = 400msec)

here are some screen shots. Also I include in attachment the registers configured.

We not intend to enable the options for either 1. Lead Off Detection or 2. RLD corrective common mode signal

Any ideas why this is happening?

=======================================

=======================================

=====================================

========================================================

========================================================

// ADS1299_REG__ID_ADD

0x00,

// ADS1299_REG__CONFIG1_ADD //0xB4,

(ADS1299_REG__CONFIG1__ALWAYS_WRITE |

(ADS1299_REG__CONFIG1__DR__FMOD_1024 << ADS1299_REG__CONFIG1__DR_SHIFT) |

(ADS1299_REG__CONFIG1__CLK_EN__ENABLE << ADS1299_REG__CONFIG1__CLK_EN_SHIFT) |

(ADS1299_REG__CONFIG1__DAISY_EN__DAISY << ADS1299_REG__CONFIG1__DAISY_EN_SHIFT)),

// ADS1299_REG__CONFIG2_ADD // 0xD4

(ADS1299_REG__CONFIG2__ALWAYS_WRITE |

(ADS1299_REG__CONFIG2__CAL_FREQ__LOW << ADS1299_REG__CONFIG2__CAL_FREQ_SHIFT) |

(ADS1299_REG__CONFIG2__CAL_AMP__LOW << ADS1299_REG__CONFIG2__CAL_AMP_SHIFT) |

(ADS1299_REG__CONFIG2__INT_CAL__INTERNAL << ADS1299_REG__CONFIG2__INT_CAL_SHIFT)),

// ADS1299_REG__CONFIG3 // 0xED

(ADS1299_REG__CONFIG3__ALWAYS_WRITE |

(ADS1299_REG__CONFIG3__BIAS_LOFF_SENS__DISABLE << ADS1299_REG__CONFIG3__BIAS_LOFF_SENS_SHIFT) |

(ADS1299_REG__CONFIG3__PD_BIAS__BIAS_ON << ADS1299_REG__CONFIG3__PD_BIAS_SHIFT) |

(ADS1299_REG__CONFIG3__BIASREF_INT__INTERNAL << ADS1299_REG__CONFIG3__BIASREF_INT_SHIFT) |

(ADS1299_REG__CONFIG3__BIAS_MEAS__OPEN << ADS1299_REG__CONFIG3__BIAS_MEAS_SHIFT) |

(ADS1299_REG__CONFIG3__PD_REFBUF__REFBUF_ON << ADS1299_REG__CONFIG3__PD_REFBUF_SHIFT)),

// ADS1299_REG__LOFF // 0x00

((ADS1299_REG__LOFF__FLEAD_OFF__DC << ADS1299_REG__LOFF__FLEAD_OFF_SHIFT) |

(ADS1299_REG__LOFF__ILEAD_OFF__6NA << ADS1299_REG__LOFF__ILEAD_OFF_SHIFT) |

(ADS1299_REG__LOFF__COMP_TH__5__95 << ADS1299_REG__LOFF__COMP_TH_SHIFT)),

// ADS1299_REG__CH1SET // 0x60

((ADS1299_REG__CHNSET__MUX__NORMAL << ADS1299_REG__CHNSET__MUX_SHIFT) |

// ((ADS1299_REG__CHNSET__MUX__TEST << ADS1299_REG__CHNSET__MUX_SHIFT) |

(ADS1299_REG__CHNSET__SRB2__OPEN << ADS1299_REG__CHNSET__SRB2_SHIFT) |

(ADS1299_REG__CHNSET__GAIN__24 << ADS1299_REG__CHNSET__GAIN_SHIFT) |

(ADS1299_REG__CHNSET__PD__NORMAL << ADS1299_REG__CHNSET__PD_SHIFT)),

// ADS1299_REG__CH2SET // 0x60

((ADS1299_REG__CHNSET__MUX__NORMAL << ADS1299_REG__CHNSET__MUX_SHIFT) |

// ((ADS1299_REG__CHNSET__MUX__TEST << ADS1299_REG__CHNSET__MUX_SHIFT) |

(ADS1299_REG__CHNSET__SRB2__OPEN << ADS1299_REG__CHNSET__SRB2_SHIFT) |

(ADS1299_REG__CHNSET__GAIN__24 << ADS1299_REG__CHNSET__GAIN_SHIFT) |

(ADS1299_REG__CHNSET__PD__NORMAL << ADS1299_REG__CHNSET__PD_SHIFT)),

// ADS1299_REG__CH3SET // 0x60

((ADS1299_REG__CHNSET__MUX__NORMAL << ADS1299_REG__CHNSET__MUX_SHIFT) |

// ((ADS1299_REG__CHNSET__MUX__TEST << ADS1299_REG__CHNSET__MUX_SHIFT) |

(ADS1299_REG__CHNSET__SRB2__OPEN << ADS1299_REG__CHNSET__SRB2_SHIFT) |

(ADS1299_REG__CHNSET__GAIN__24 << ADS1299_REG__CHNSET__GAIN_SHIFT) |

(ADS1299_REG__CHNSET__PD__NORMAL << ADS1299_REG__CHNSET__PD_SHIFT)),

// ADS1299_REG__CH4SET // 0x60

((ADS1299_REG__CHNSET__MUX__NORMAL << ADS1299_REG__CHNSET__MUX_SHIFT) |

// ((ADS1299_REG__CHNSET__MUX__TEST << ADS1299_REG__CHNSET__MUX_SHIFT) |

(ADS1299_REG__CHNSET__SRB2__OPEN << ADS1299_REG__CHNSET__SRB2_SHIFT) |

(ADS1299_REG__CHNSET__GAIN__24 << ADS1299_REG__CHNSET__GAIN_SHIFT) |

(ADS1299_REG__CHNSET__PD__NORMAL << ADS1299_REG__CHNSET__PD_SHIFT)),

// ADS1299_REG__CH5SET // 0x60

((ADS1299_REG__CHNSET__MUX__NORMAL << ADS1299_REG__CHNSET__MUX_SHIFT) |

// ((ADS1299_REG__CHNSET__MUX__TEST << ADS1299_REG__CHNSET__MUX_SHIFT) |

(ADS1299_REG__CHNSET__SRB2__OPEN << ADS1299_REG__CHNSET__SRB2_SHIFT) |

(ADS1299_REG__CHNSET__GAIN__24 << ADS1299_REG__CHNSET__GAIN_SHIFT) |

(ADS1299_REG__CHNSET__PD__NORMAL << ADS1299_REG__CHNSET__PD_SHIFT)),

// ADS1299_REG__CH6SET // 0x60

((ADS1299_REG__CHNSET__MUX__NORMAL << ADS1299_REG__CHNSET__MUX_SHIFT) |

// ((ADS1299_REG__CHNSET__MUX__TEST << ADS1299_REG__CHNSET__MUX_SHIFT) |

(ADS1299_REG__CHNSET__SRB2__OPEN << ADS1299_REG__CHNSET__SRB2_SHIFT) |

(ADS1299_REG__CHNSET__GAIN__24 << ADS1299_REG__CHNSET__GAIN_SHIFT) |

(ADS1299_REG__CHNSET__PD__NORMAL << ADS1299_REG__CHNSET__PD_SHIFT)),

// ADS1299_REG__CH7SET // 0x60

((ADS1299_REG__CHNSET__MUX__NORMAL << ADS1299_REG__CHNSET__MUX_SHIFT) |

// ((ADS1299_REG__CHNSET__MUX__TEST << ADS1299_REG__CHNSET__MUX_SHIFT) |

(ADS1299_REG__CHNSET__SRB2__OPEN << ADS1299_REG__CHNSET__SRB2_SHIFT) |

(ADS1299_REG__CHNSET__GAIN__24 << ADS1299_REG__CHNSET__GAIN_SHIFT) |

(ADS1299_REG__CHNSET__PD__NORMAL << ADS1299_REG__CHNSET__PD_SHIFT)),

// ADS1299_REG__CH8SET // 0x60

((ADS1299_REG__CHNSET__MUX__NORMAL << ADS1299_REG__CHNSET__MUX_SHIFT) |

// ((ADS1299_REG__CHNSET__MUX__TEST << ADS1299_REG__CHNSET__MUX_SHIFT) |

(ADS1299_REG__CHNSET__SRB2__OPEN << ADS1299_REG__CHNSET__SRB2_SHIFT) |

(ADS1299_REG__CHNSET__GAIN__24 << ADS1299_REG__CHNSET__GAIN_SHIFT) |

(ADS1299_REG__CHNSET__PD__NORMAL << ADS1299_REG__CHNSET__PD_SHIFT)),

// ADS1299_REG__BIAS_SENSP // 0x00

// (0x01 | 0x02 | 0x04 | 0x10 | 0x40),

0xFF,

// ADS1299_REG__BIAS_SENSN // 0x00

// (0x08 | 0x20),

0xFF,

// ADS1299_REG__LOFF_SENSP // 0x00

// (0x01 | 0x02 | 0x04 | 0x10 | 0x40),

0x00,

// ADS1299_REG__LOFF_SENSN // 0x00

// (0x08 | 0x20),

0x00,

// ADS1299_REG__LOFF_FLIP // 0x00

// (0x08 | 0x20),

0x00,

// ADS1299_REG__LOFF_STATP // 0x00

0x00,

// ADS1299_REG__LOFF_STATN // 0x00

0x00,

// ADS1299_REG__GPIO // 0x0F

0x0F,

// ADS1299_REG__MISC1 // 0x00

((ADS1299_REG__MISC1__SRB1__OPEN << ADS1299_REG__MISC1__SRB1_SHIFT)),

// ADS1299_REG__MISC2 // 0x00

0x00,

// ADS1299_REG__CONFIG4 // 0x00

((ADS1299_REG__CONFIG4__PD_LOFF_COMP__COMP_ON << ADS1299_REG__CONFIG4__PD_LOFF_COMP_SHIFT) |

(ADS1299_REG__CONFIG4__SINGLE_SHOT__CONTINUOUS << ADS1299_REG__CONFIG4__SINGLE_SHOT_SHIFT))

============================================================