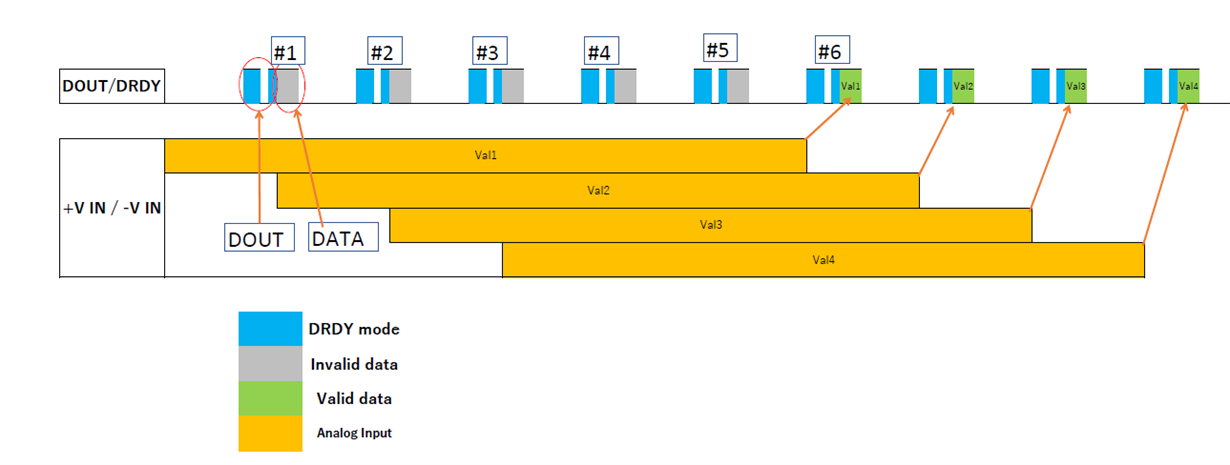

For the convenience of the system, we are thinking of acquiring data in 1tDRDY cycle.

(Of course, 5 cycles after start-up are discarded.)

We hope the evidence that there is no problem even if only the 6th cycle data is applied as valid data.

Although there is a description of the conversion cycle in the data sheet, there is no description of what timing the analog value becomes the conversion data, so I asked such a question.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.