Hi sir,

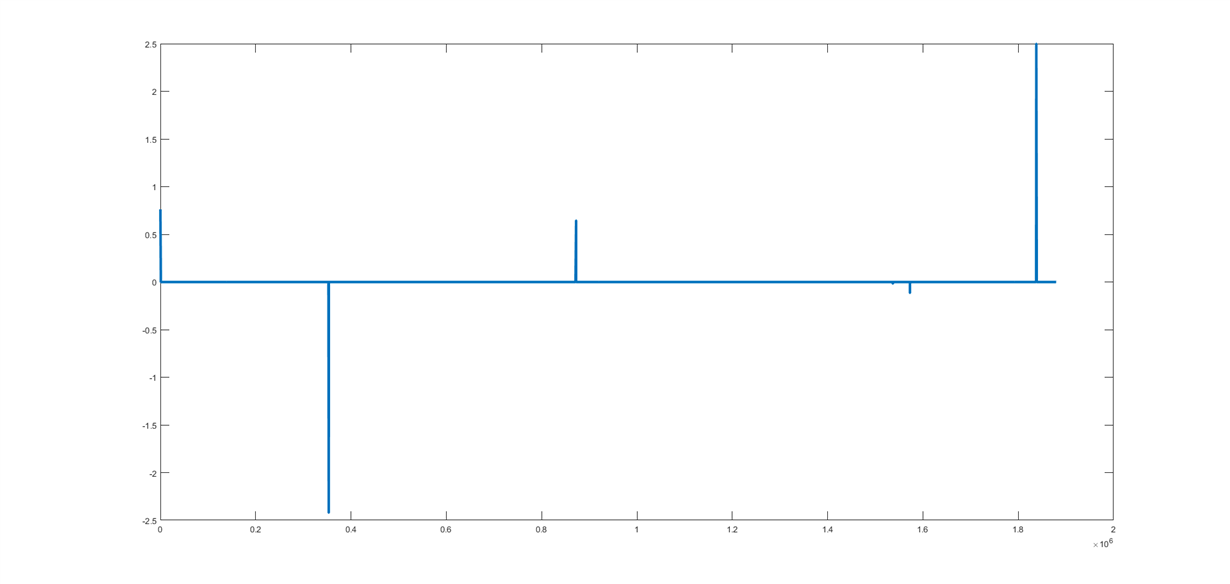

There are some jump points when data convering. I have changed the data rate from 20sps,100sps, 400sps and filter types, but the issue still exist. The jump point is only one sample point at any time. The following figure is 400sps, sinc4 filter. and GND input.

Please help me, i have no idea anyway. Thank you and godness.