Greetings,

I have several devices on an I2C bus, all certified to run at 400kHz, except for the AMC6821. While the data sheet for the AMC6821 says that 100kHz is the maximum frequency, has anyone run it at 400kHz or even 200kHz?

Thanks,

Jeff

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Jeff,

This is a very good question. Are you currently using a 400 KHz I2C clock to communicate to the AMC6821?

Although the datasheet has 100 KHz as the maximum I2C clock, it might be possible to run it in fast mode. We haven’t tried it, yet. However, it is difficult to know the effects on performance since all characterization was done with a 100 KHz I2C clock. Besides, it might be possible that some parts work in fast mode and others don’t. I will look into it and let you know once I check with the design crew.

Regards,

Hello Jeff,

After discussing with design group, it was noticed that, with a 400 KHz SCLK, the AMC6821 can have problems identifying the start and stop bits from the master, which is why it has a maximum spec of 100 KHz for SCLK.

If the start bit were to be identified, the AMC6821 would be able to send and receive bytes because data hold and setup times are small enough for a 400 KHz SCLK. However, after sending or receiving anything, the stop bit must be identified. If the AMC6821 doesn’t identify the stop bit, it can corrupt all data in the bus from or to other parts.

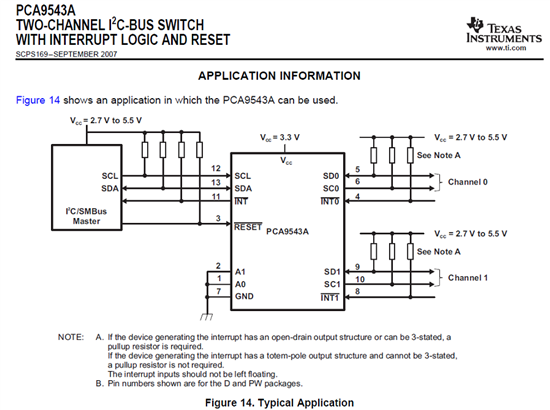

The best solution is to use a 100KHz SCLK for all devices or use a I2C MUX like the PCA9543A to separate the AMC6821 when the master uses 400KHz SCLK.

Regards,