Other Parts Discussed in Thread: ADS54J64, LMK04828

Hello,

My customer is planning to connect ADS54J64EVM to their FPGA board via the FMC connector.

And as a practice, they tried to operate ADS54J64EVM itself without TSW14J56EVM or their FPGA board.

According to ADS54J64 Evaluation Module User’s Guide 2.3.1, they follow the following step #1 to #3.

1. Open the ADS54J64EVM GUI from the Start Menu → All Programs → Texas Instruments →

ADS54J64 EVM.

2. After the GUI starts, verify that the green USB Status indicator in the top right corner of the GUI is

illuminated.

3. From the INTRO tab, press the Configure LMK04828 button labeled as "Fclk=983.04MHz".

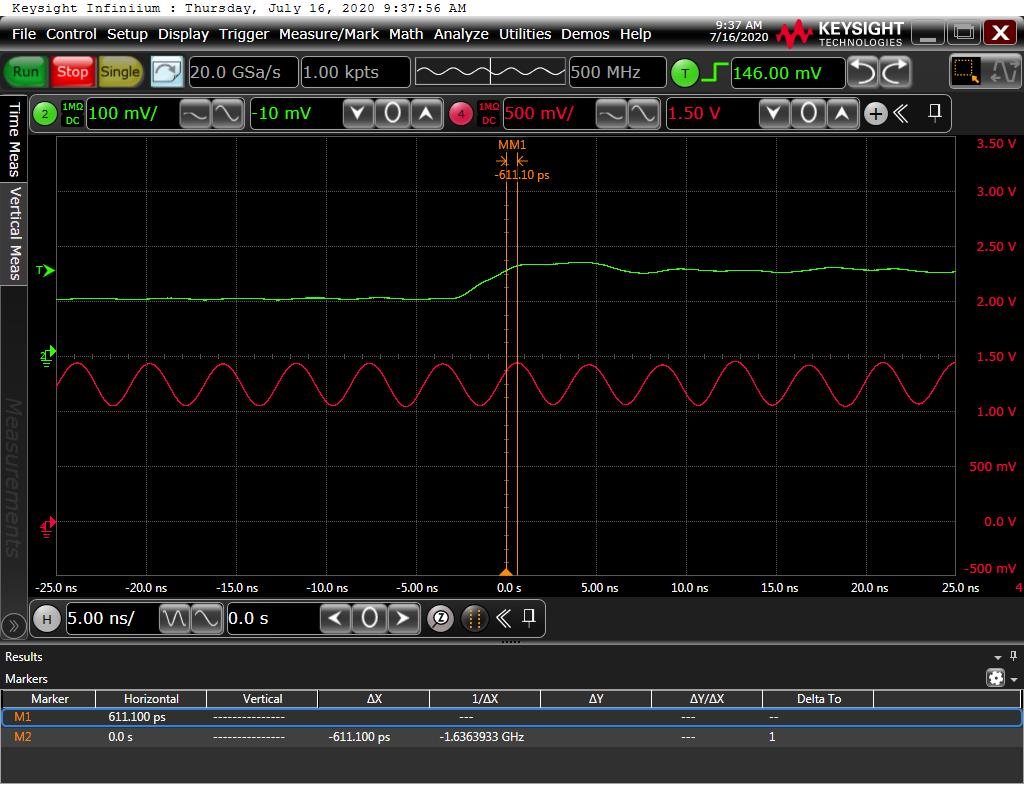

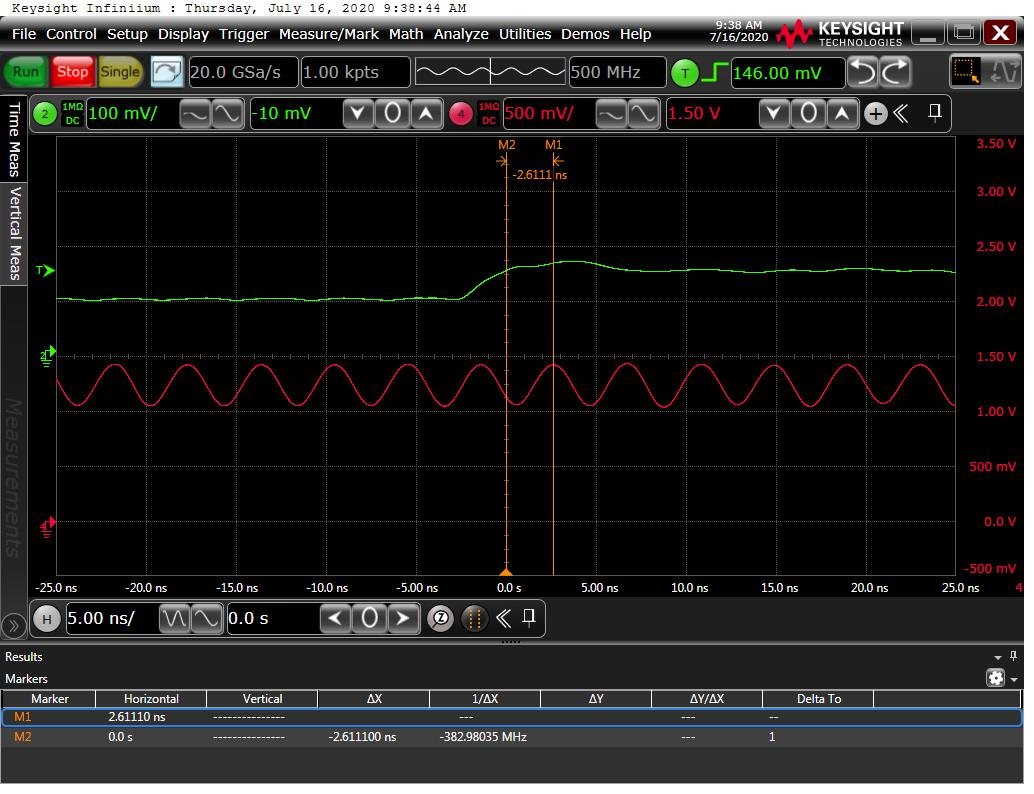

After that, they observed DCLKOUT0(device clock) and SDCLKOUT1(sysref) by oscilloscope.

The phase relationship between them are different every power cycle.

They expected the fixed constant phase relationship between them because they are JESD device clock and sysref.

Why their phase relationship is not deterministic? What is wrong?

To get the deterministic phase relation between the, what does my customer have to do?

Best regards,

K.Hirano