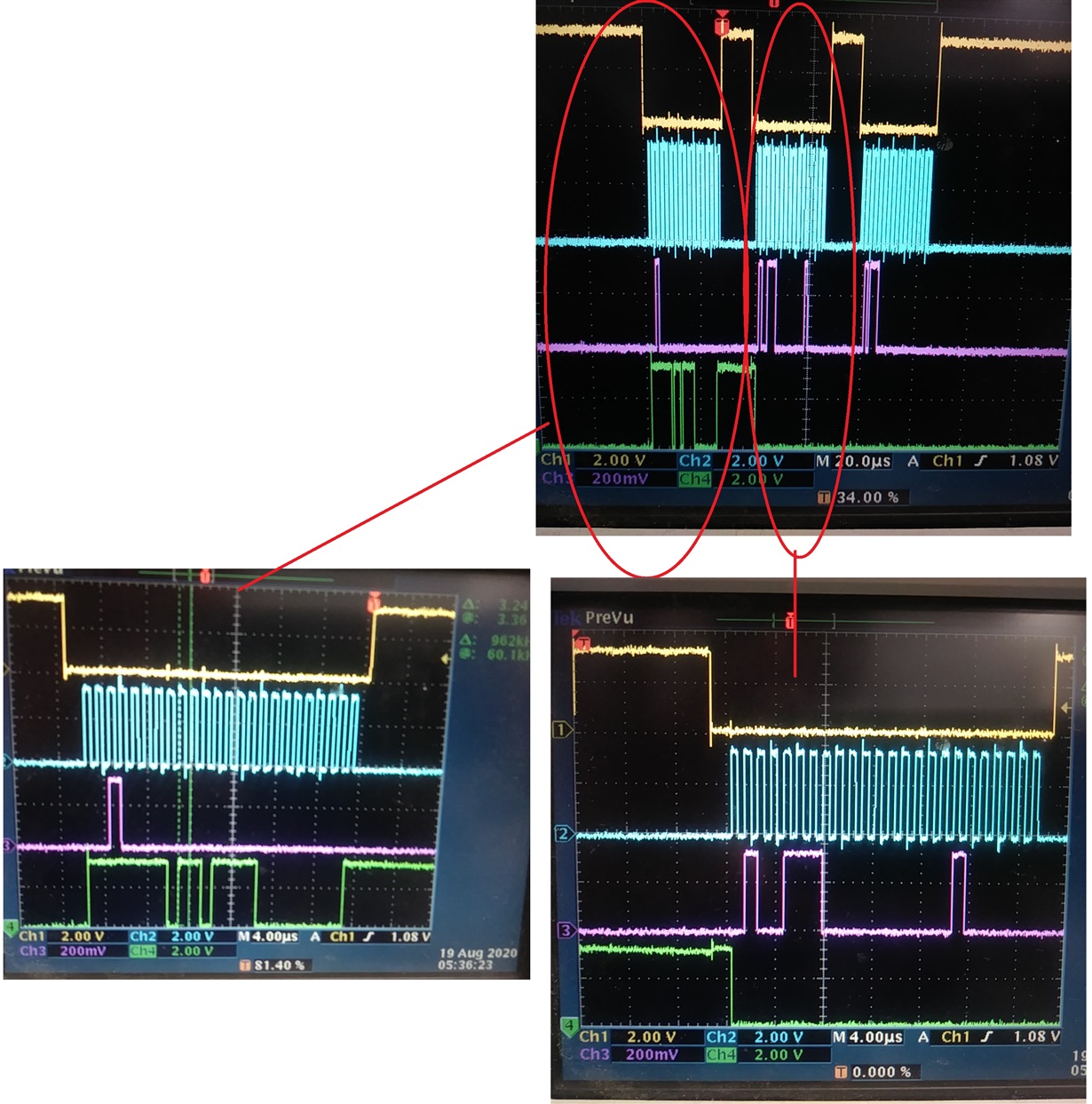

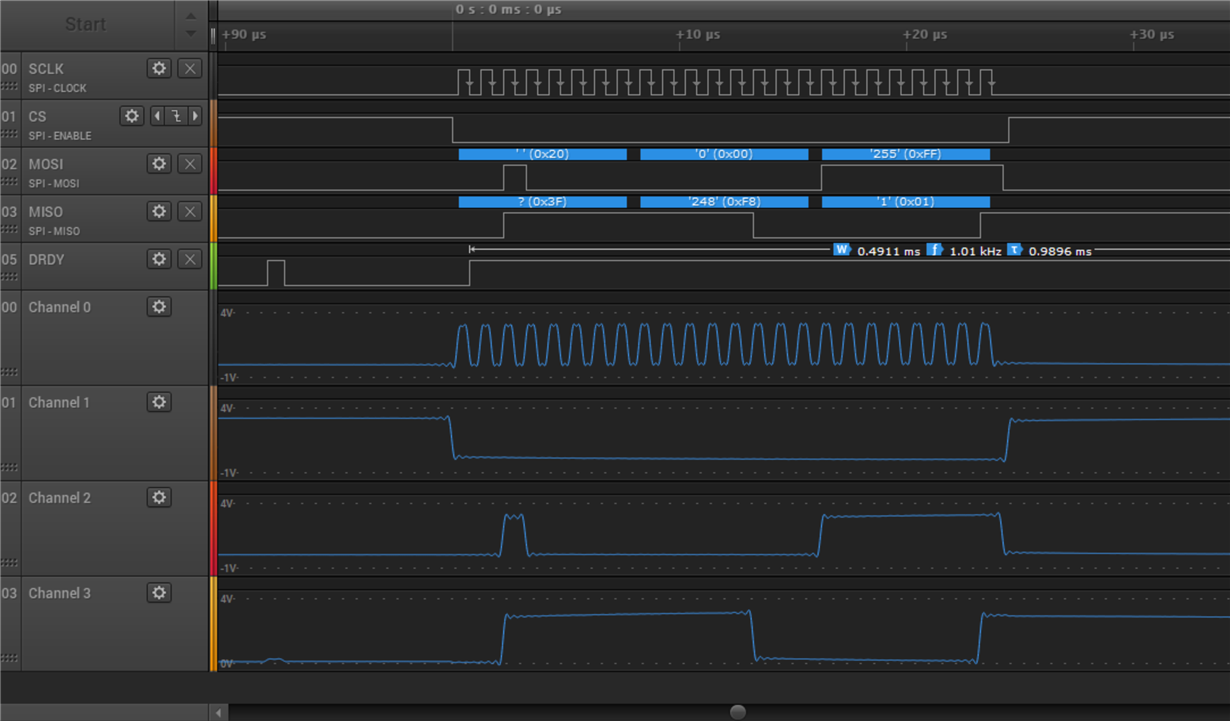

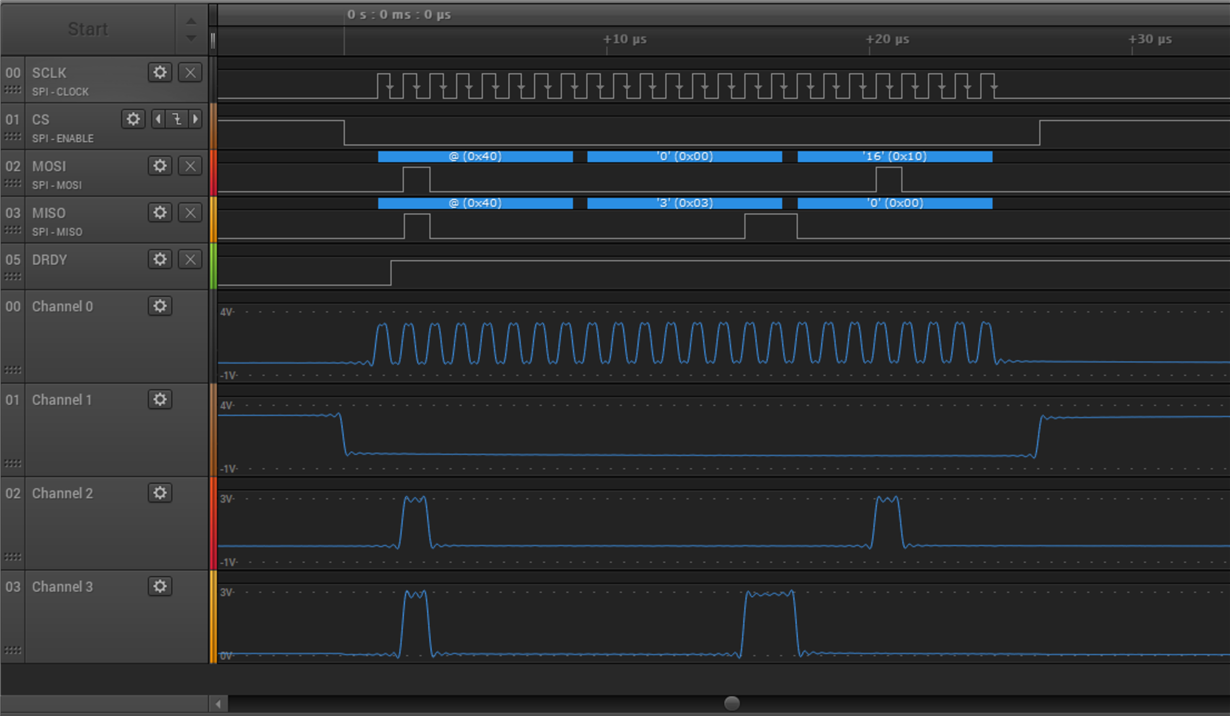

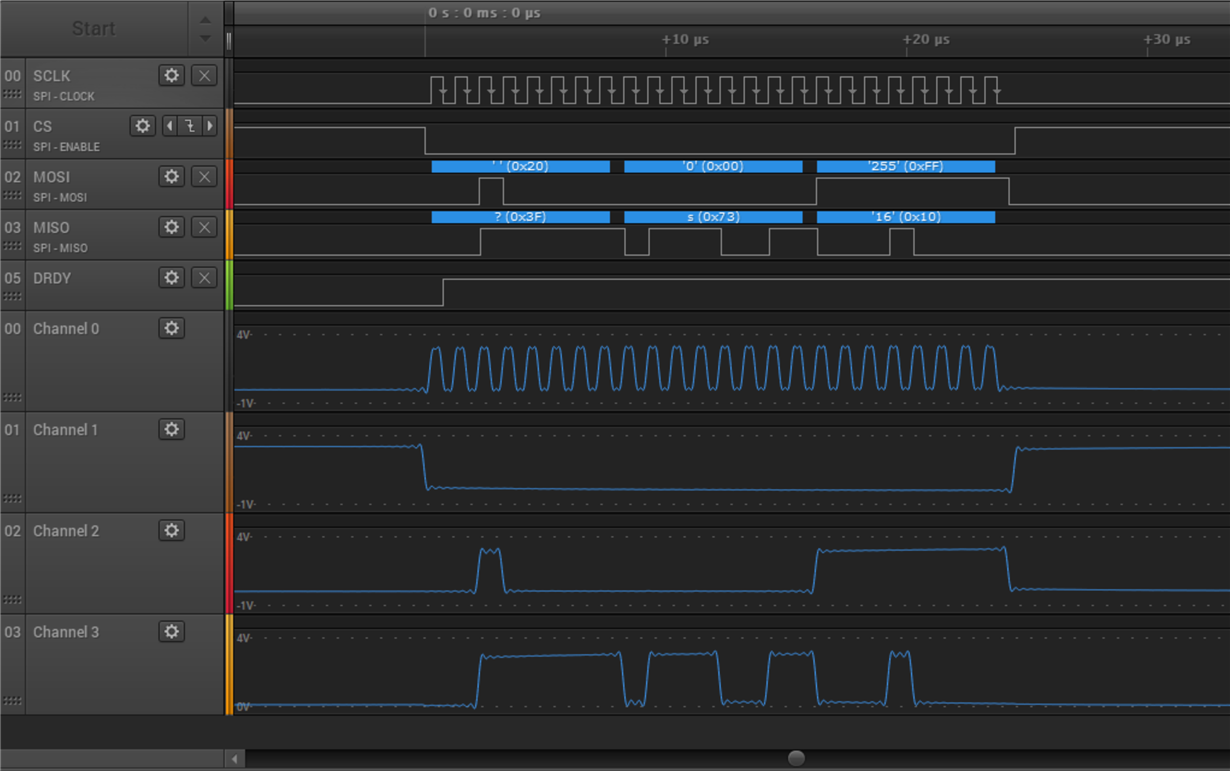

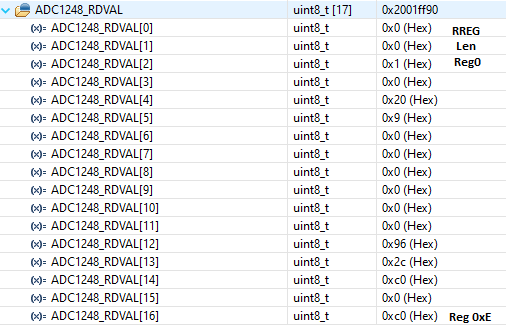

We've just received our ADS1248 boards that measures 2 differential voltages (AIN0/AIN1, AIN4/AIN5) and 2 RTDs (AIN2/AIN3 , AIN6/AIN7 ). For testing, I've placed 1.5k resistors on the RTD inputs.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.